A Low Area Overhead NBTI/PBTI Sensor for SRAM Memories

Product Description

A Low Area Overhead NBTI/PBTI Sensor for SRAM Memories

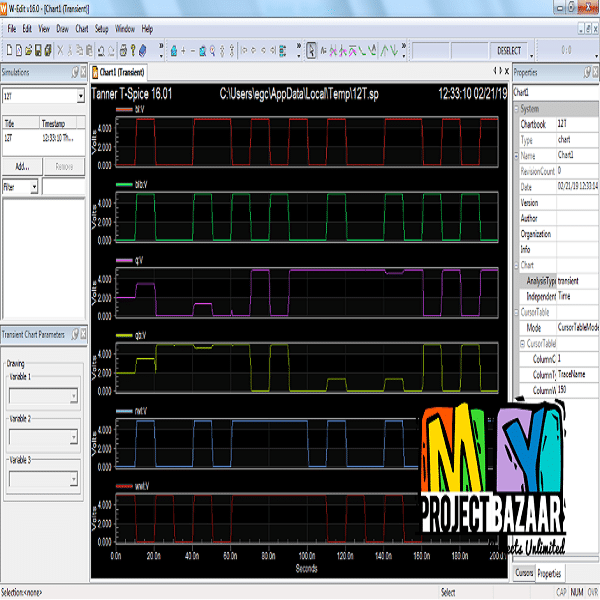

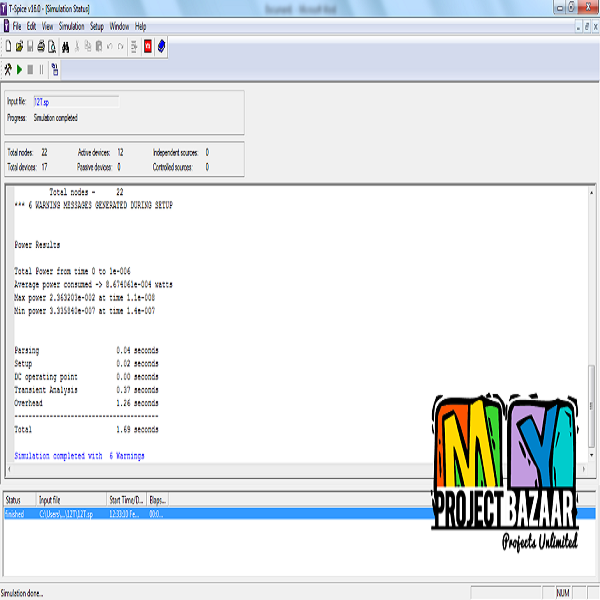

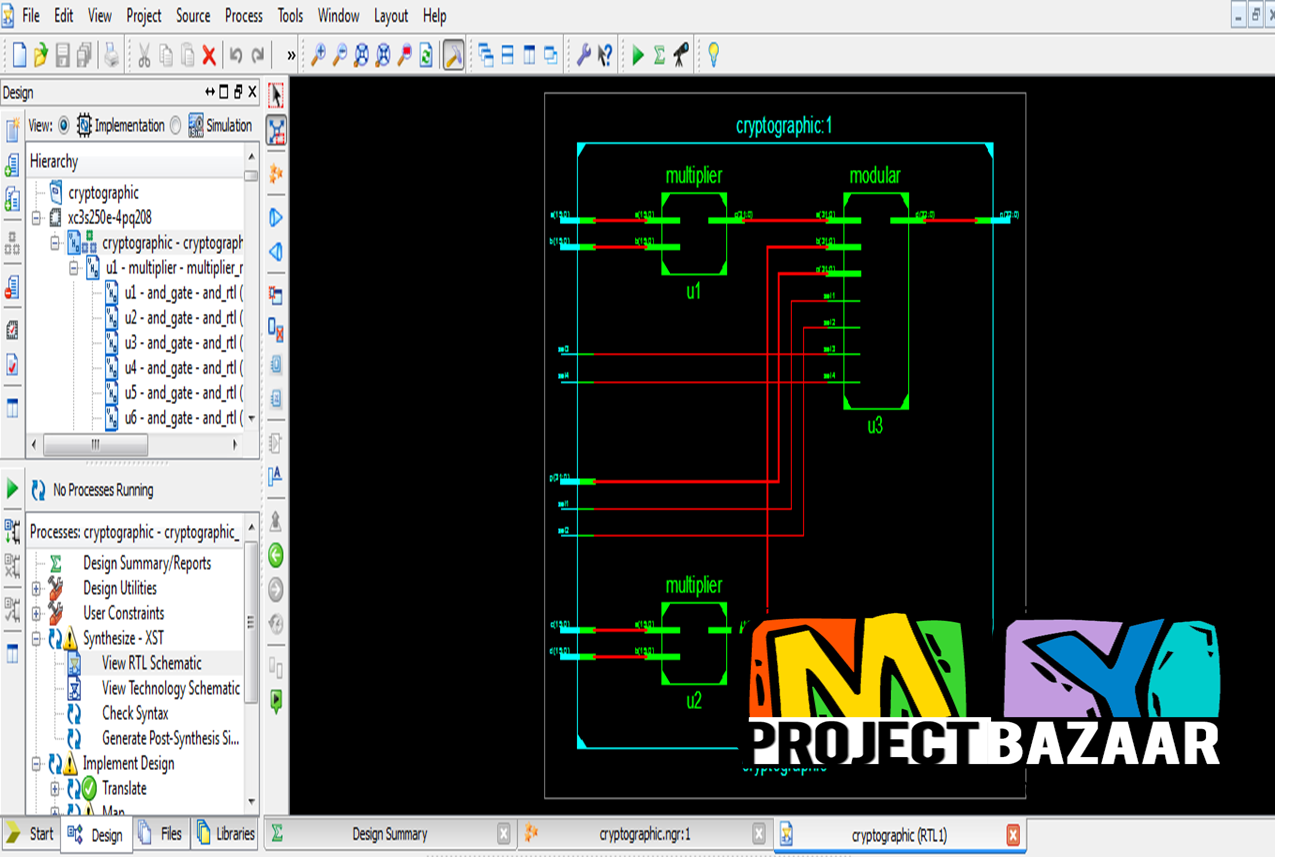

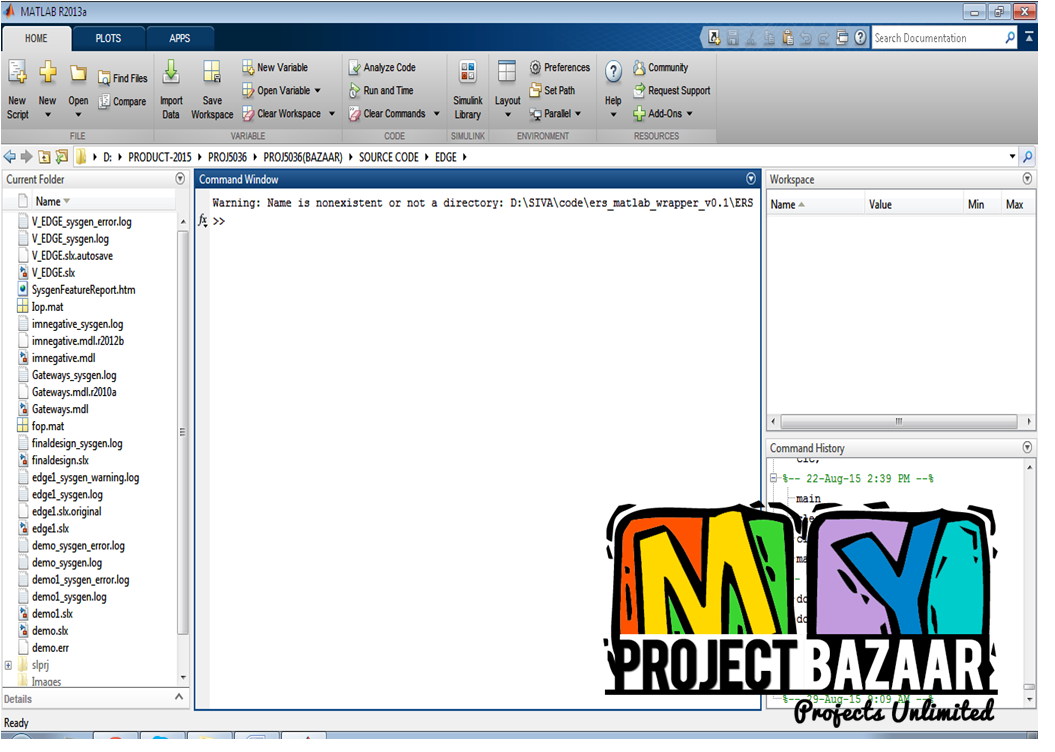

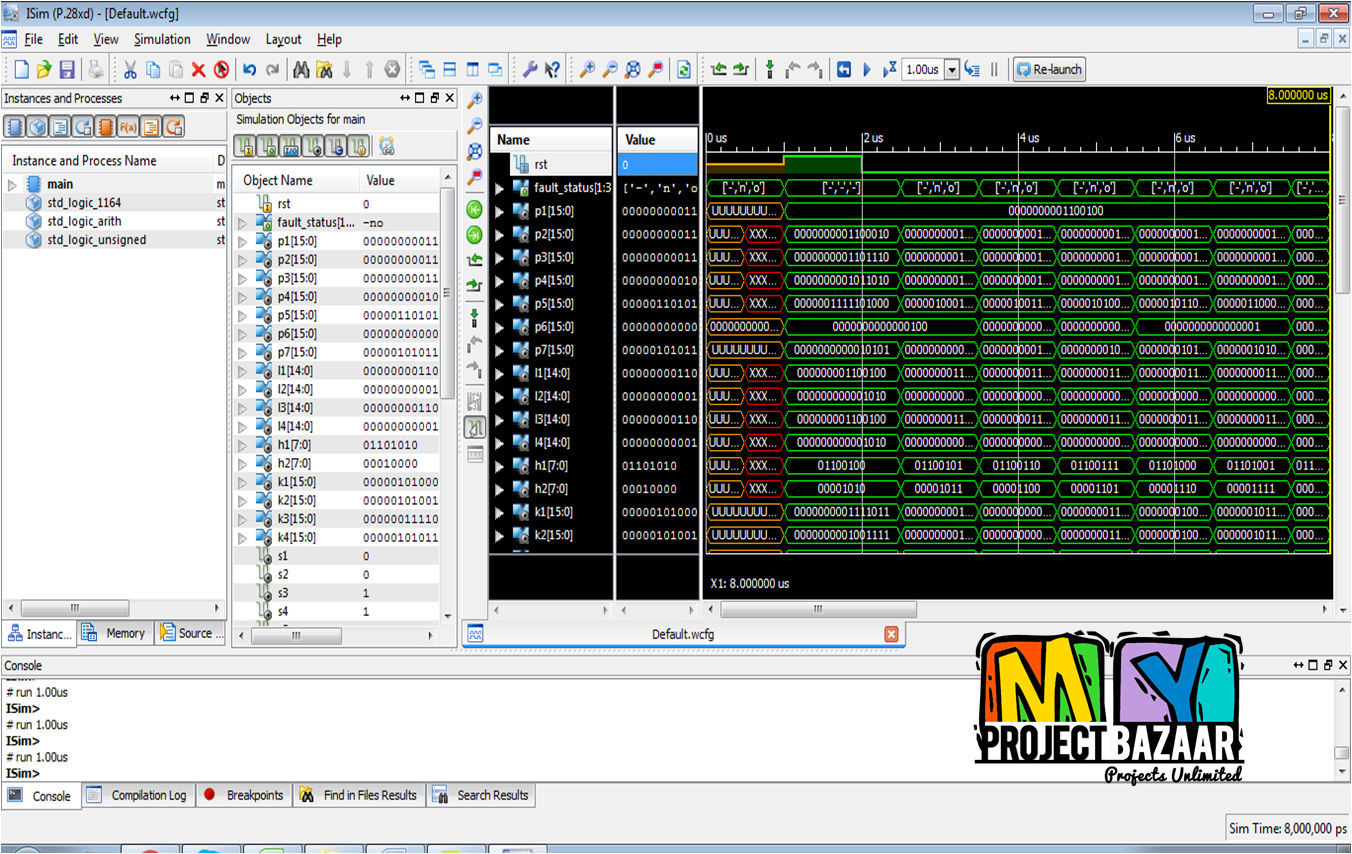

Abstract-Bias temperature instability (BTI) is known as one serious reliability concern in nanoscale technologies. BTI gradually increases the absolute value of threshold voltage (Vth) of MOS transistors. The main consequence of Vth shift of the SRAM cell transistors is the static noise margin (SNM) degradation. The SNM degradation of SRAM cells results in bit-flip occurrences due to transient faults and should be monitored accurately. This paper proposes a sensor called write current-based BTI sensor (WCBS) to assess the BTI-aging state of SRAM cells. The WCBS measures BTI-induced SNM degradation of SRAM cells by monitoring the maximum write current shifts due to BTI. The observations show that the maximum current consumption during write operation is an effective identifier to measure Vth and SNM shifts. The granularity of BTI assessment of one cell up to a row of memory can be achieved by writing special bit patterns on the memory block during the test. We evaluated

the sensor through SPICE-level simulations in 32-nm technology size. The precision of WCBS is about ±1.25 mV (±3.2% error). One sensor is enough for the entire SRAM memory block with negligible area/power overhead; less than 1%. The effects of process variation and temperature changes on WCBS are investigated in detail.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+