TOWARD MULTI-GIGABIT WIRELESS: DESIGN OF HIGH-THROUGHPUT MIMO DETECTORS WITH HARDWARE-EFFICIENT ARCHITECTURE

Product Description

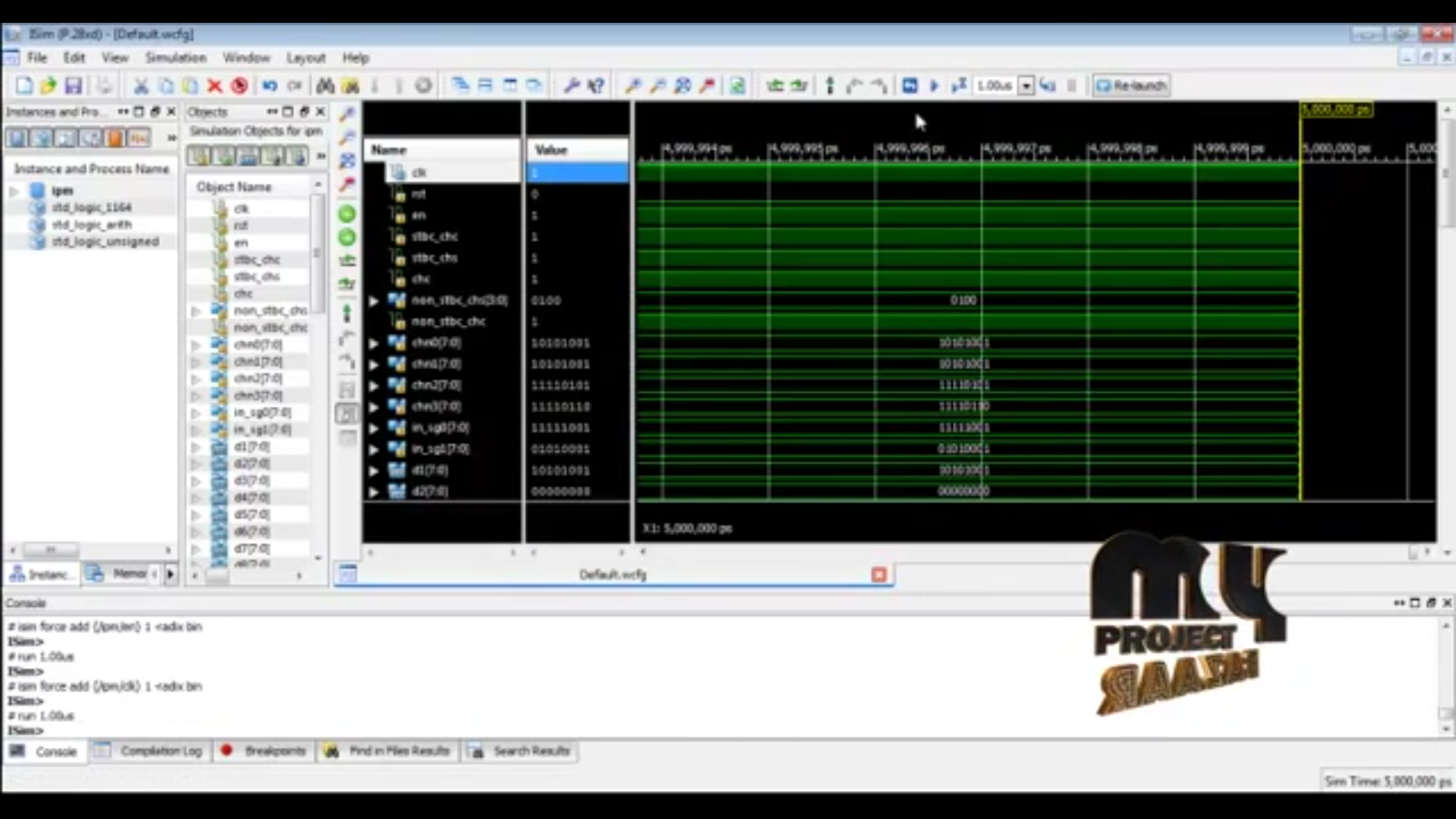

Abstract—This paper presents a hardware-efficient architecture for 4×4 and 8×8 high-throughput MIMO detectors. The adopted non-constant K-best algorithm tends to keep more survival nodes in top search tree layers and reduce computational complexity in bottom layers as opposed to the conventional K-best algorithm. A pipelined architecture is used to generate one detection output per clock cycle, thus meeting multi-gigabit throughput requirements for advanced wireless communication systems. The proposed efficient folding scheme strikes a suitable balance between complexity and throughput. This paper also presents a discussion on the scalability of this architecture with respect to the setting of QAM size, K values, and antenna number. < Final Year Projects > One 4×4 MIMO detector IC has been manufactured and one 8×8 MIMO detector layout has been realized, both in 90-nm CMOS technology. The 4×4 detector IC has 232 kilogates (KG). Its maximum measured throughput is 4.08 Gbps at 170-MHz operating frequency and 1.3-V core voltage. The 8×8 detector has 665 KG. Its post-layout simulation results show that it achieves 4.37-Gbps throughput at 182-MHz operating frequency and 0.9-V core voltage. Compared to earlier hard-output detectors, both implemented detectors demonstrate good normalized power and normalized hardware efficiencies.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet