Subthreshold Dual Mode Logic

Product Description

Subthreshold Dual Mode Logic

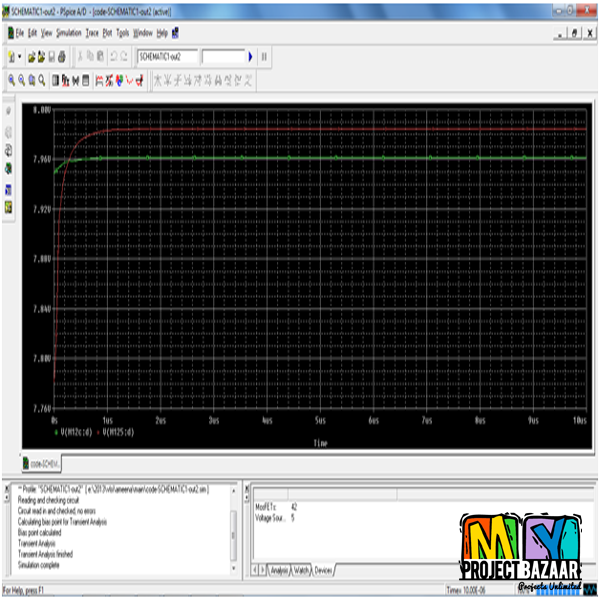

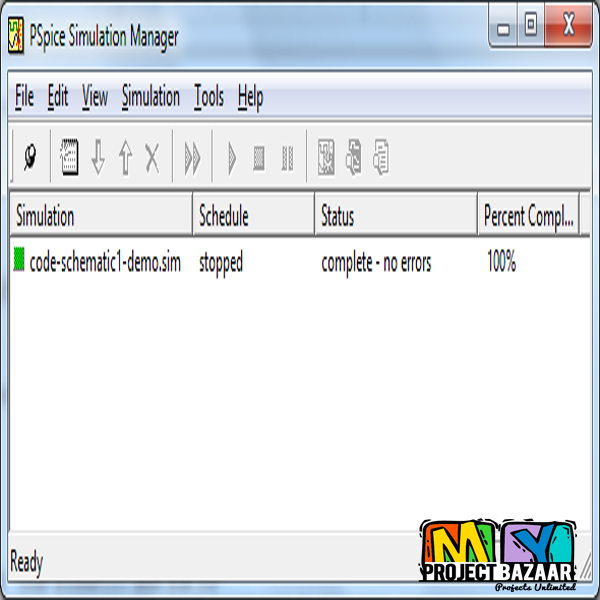

Abstract-Subthreshold Dual Mode Logic. In this brief, we introduce a novel low-power dual mode logic (DML) family, designed to operate in the subthreshold region. The proposed logic family can be switched between static and dynamic modes of operation according to system requirements. In static mode, the DML gates feature very low-power dissipation with moderate performance, while in dynamic mode they achieve higher performance, < Final Year Projects > albeit with increased power dissipation. This is achieved with a simple and intuitive design concept. SPICE and Monte Carlo simulations compare performance, power dissipation, and robustness of the proposed DML gates to their CMOS and domino counterparts in the 80-nm process. Measurements of an 80-nm test chip are presented in order to prove the proposed concept.

Including Packages

Our Specialization

Support Service

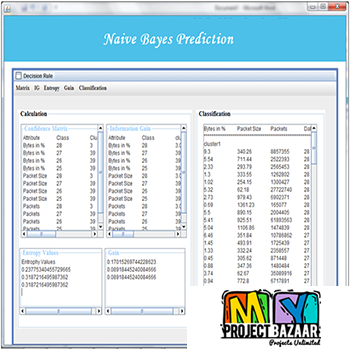

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet