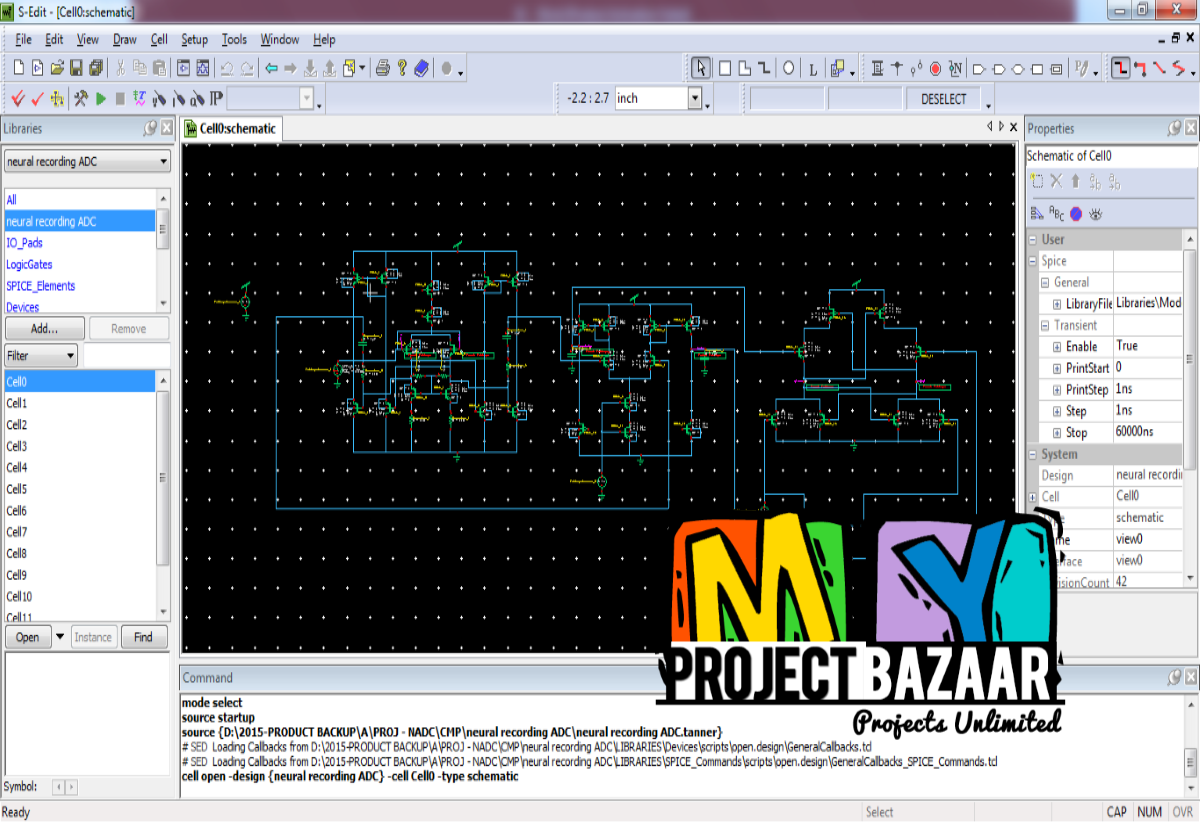

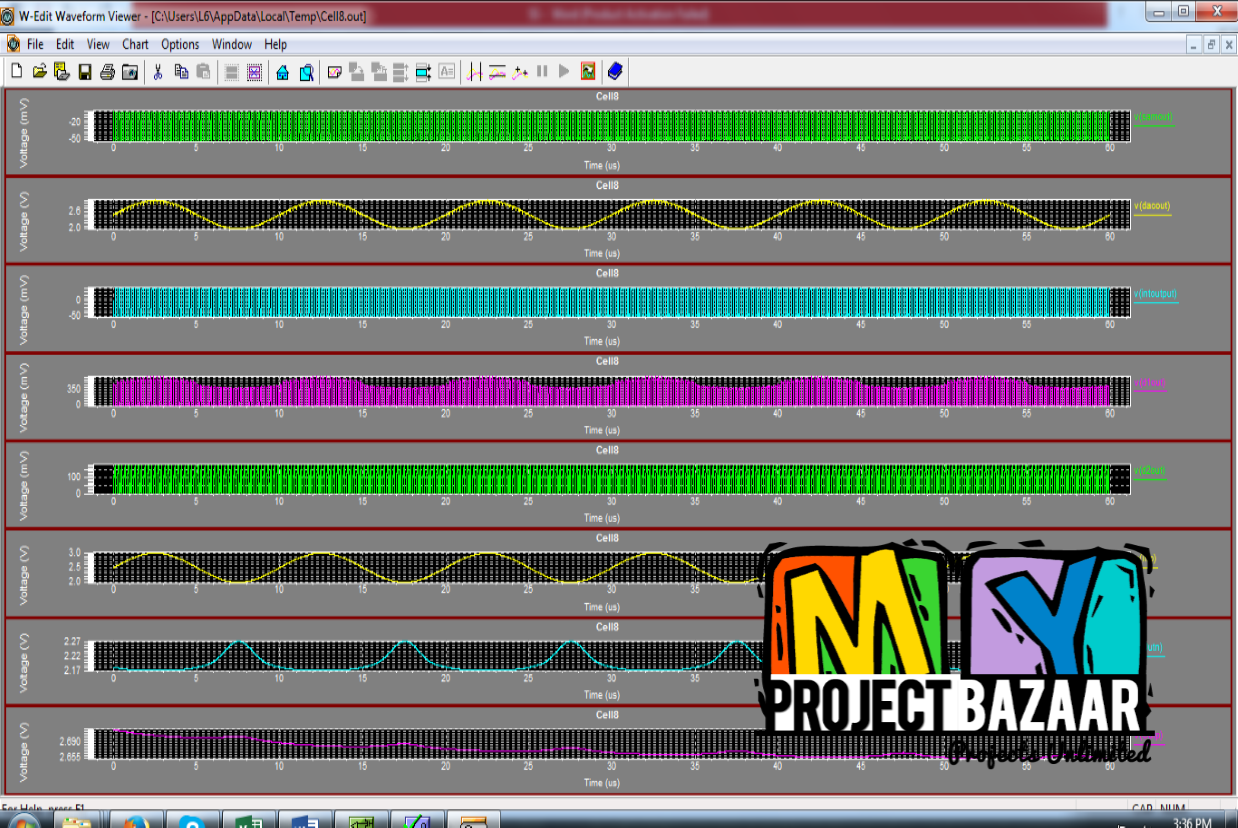

A Power-Efficient Continuous-Time Incremental Sigma-Delta ADC for Neural Recording Systems

Product Description

A Power-Efficient Continuous-Time Incremental

Sigma-Delta ADC for Neural Recording Systems

Abstract— An analog-to-digital converter (ADC) dedicated to neural recording systems. By using two continuous-time incremental sigma-delta ADCs in a pipeline configuration, the proposed ADC can achieve high-resolution without sacrificing the conversion rate. This two-step architecture is also power-efficient, as the resolution requirement for the incremental sigma-delta ADC in each step is significantly relaxed. To further enhance the power efficiency, a class-AB output stage and a dynamic summing comparator are used to implement the sigma-delta modulators. A prototype chip, designed and fabricated in a standard 0.18 µm CMOS process, validates the proposed ADC architecture. Measurement results show that the ADC achieves a peak signal-to-noise-plus-distortion ratio of 75.9 dB over a 4 kHz bandwidth; the power consumption is 34.8 µW, which corresponds to a figure-of-merit of 0.85 pJ/conv.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet