Low-Power Dual Dynamic Node Pulsed HybridFlip-Flop Featuring Efficient Embedded Logic

Product Description

Low-Power Dual Dynamic Node Pulsed HybridFlip-Flop Featuring Efficient Embedded Logic

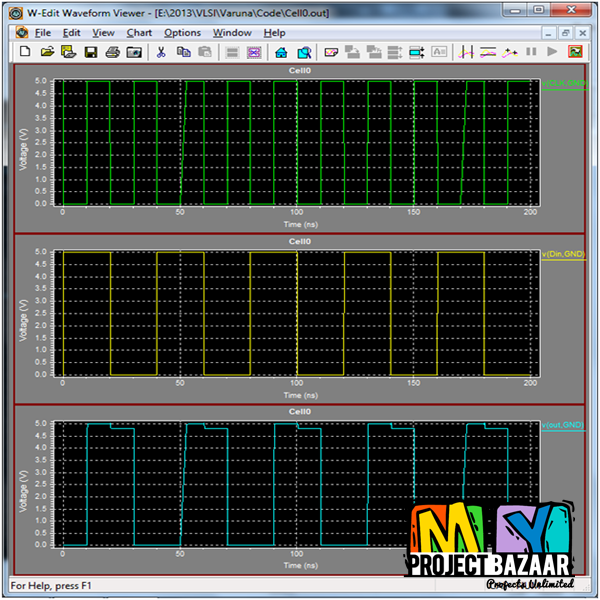

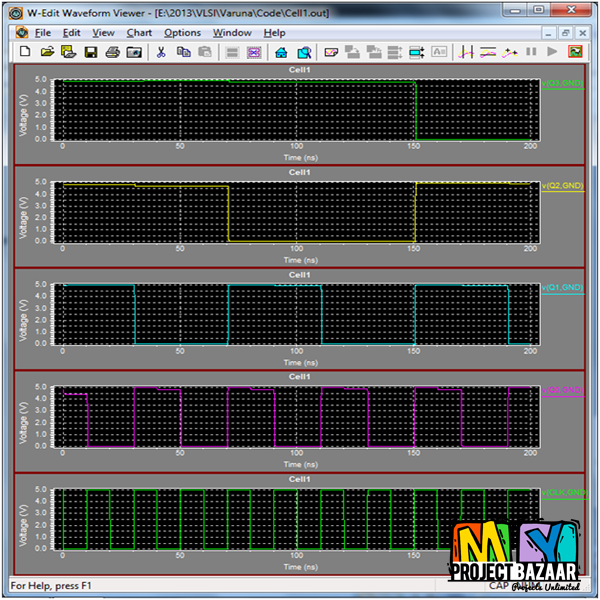

Abstract– Low-Power Dual Dynamic Node Pulsed HybridFlip-Flop Featuring Efficient Embedded Logic. In this paper, we introduce a new dual dynamic node hybrid flip-flop (DDFF) and a novel embedded logic module (DDFF-ELM) based on DDFF. The proposed designs eliminate the large capacitance present in the precharge node of several state-of-the-art designs by following a split dynamic node structure to separately drive the output pull-up and pull-down transistors. The DDFF offers a power reduction of up to 37% and 30% compared to the conventional flip-flops at 25% and 50% data activities, respectively. The aim of the DDFF-ELM is to reduce pipeline overhead. It presents an area, power, and speed efficient method to incorporate complex logic functions into the flip-flop. The performance comparisons made in a 90 nm UMC process show a power reduction of 27% compared to the Semidynamic flip-flop, < Final Year Projects > with no degradation in speed performance. The leakage power and process-voltage-temperature variations of various designs are studied in detail and are compared with the proposed designs. Also, DDFF and DDFF-ELM are compared with other state-of-the-art designs by implementing a 4-b synchronous counter and a 4-b Johnson up-down counter. The performance improvements indicate that the proposed designs are well suited for modern high-performance designs where power dissipation and latching overhead are of major concern.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet