A graph based algorithm to minimize total wire length in vlsi channel routing

Product Description

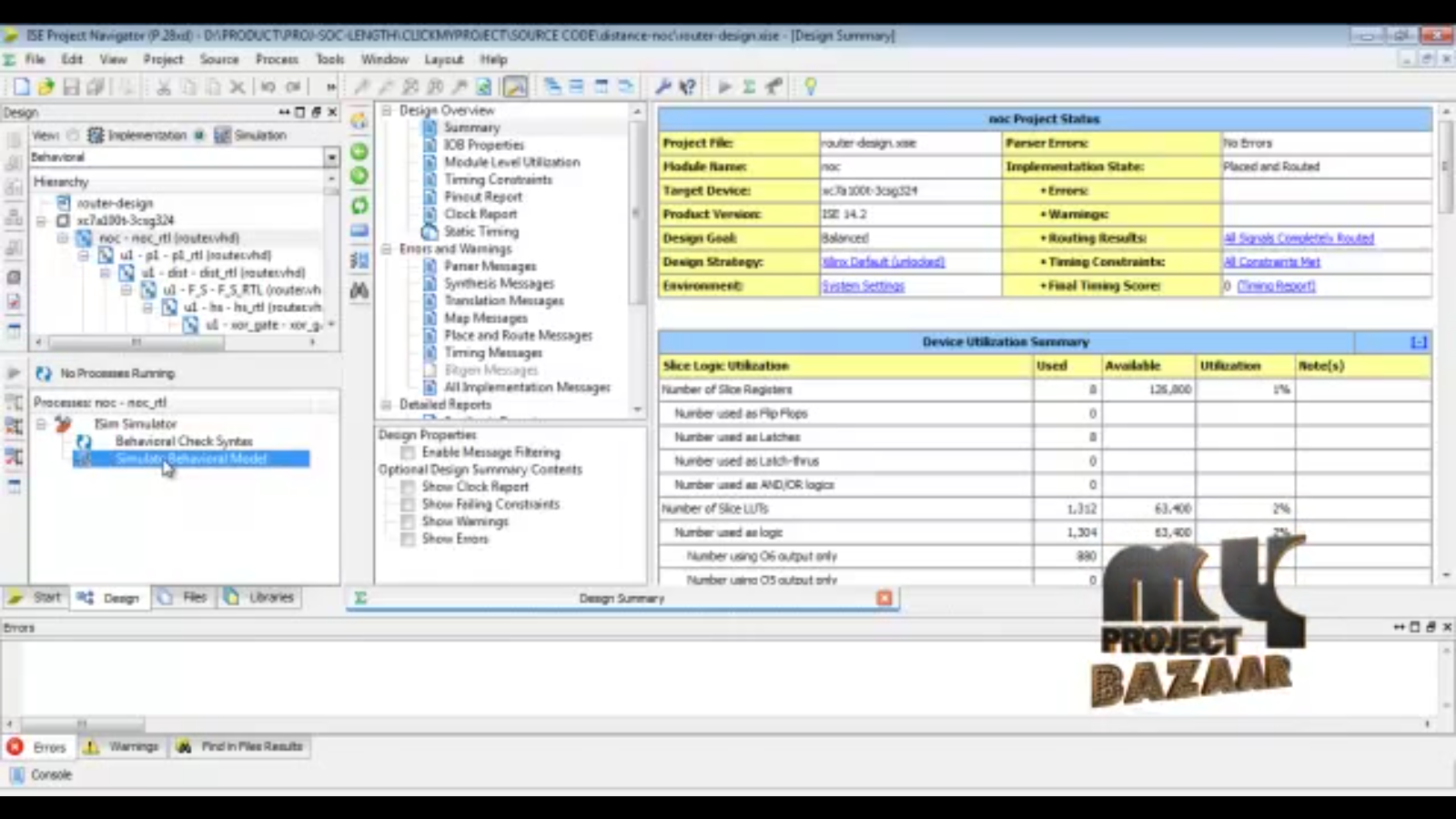

Abstract—Minimization of total (vertical) wire length is one of the most important problems in laying out blocks in VLSI physical design. Minimization of wire length not only reduces the cost of physical wiring required, but also reduces the electrical hazards of having long wires in the interconnection, power consumption, and signal propagation delays. Since the problem of computing minimum wire length routing solutions in no-dogleg, two-layer channel routing is NP-hard, < Final Year Projects > it is interesting to develop heuristic algorithms that compute routing solutions of as low total (vertical) wire length as possible. In this paper we develop an efficient heuristic algorithm for appreciably reducing the total wire length in the reserved two-layer no-dogleg Manhattan channel routing model. Experimental results obtained are greatly encouraging.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet