Design for Testability Support for Launch and Capture Power Reduction in Launch-Off-Shift and Launch-Off-Capture Testing

Product Description

Abstract—At-speed or even faster-than-at-speed testing of VLSI circuits aims for high-quality screening of the circuits by targeting performance-related faults. On one hand, a compact test set with highly effective patterns, each detecting multiple delay faults, is desirable for lower test costs. On the other hand, such patterns increase switching activity during launch and capture operations. Patterns optimized for quality and cost may thus end up violating peak-power constraints, < Final Year Projects > resulting in yield loss, while pattern generation under low switching activity constraints may lead to loss in test quality and/or pattern count inflation. In this paper, we propose design for testability (DfT) support for enabling the use of a set of patterns optimized for cost and quality as is, yet in a low power manner; we develop three different DfT mechanisms, one for launch-off shift, one for launch-off capture, and one for mixed at-speed testing. The proposed DfT support enables a design partitioning approach, where any given set of patterns, generated in a power-unaware manner, can be utilized to test the design regions one at a time, reducing both launch and capture power in a design-flow-compatible manner. This way, the test pattern count and quality of the optimized test set can be preserved, while lowering the launch/capture power.

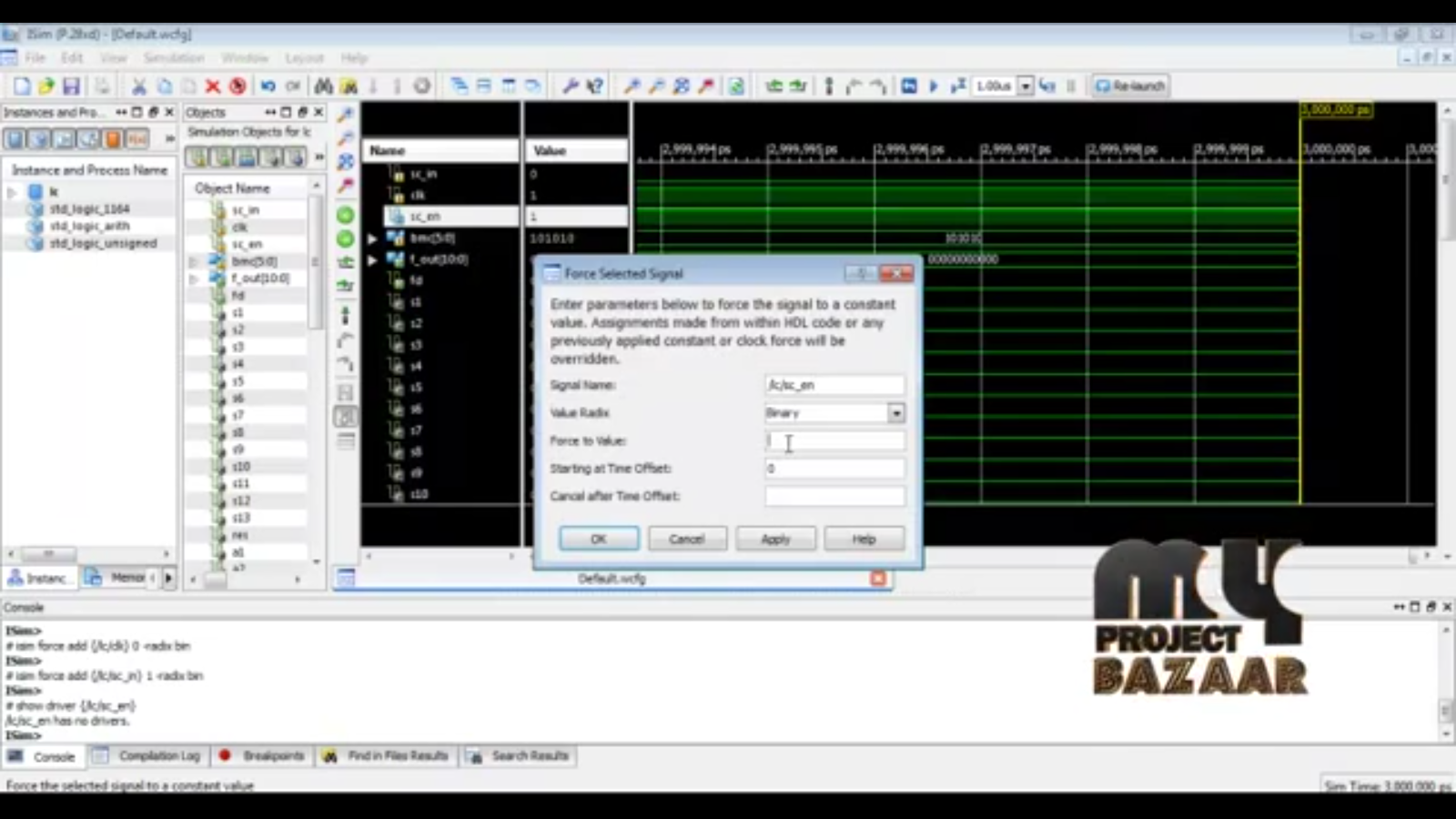

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet