A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix-2 FFT

Product Description

A Combined SDC-SDF Architecture for Normal I/O Pipelined Radix-2 FFT

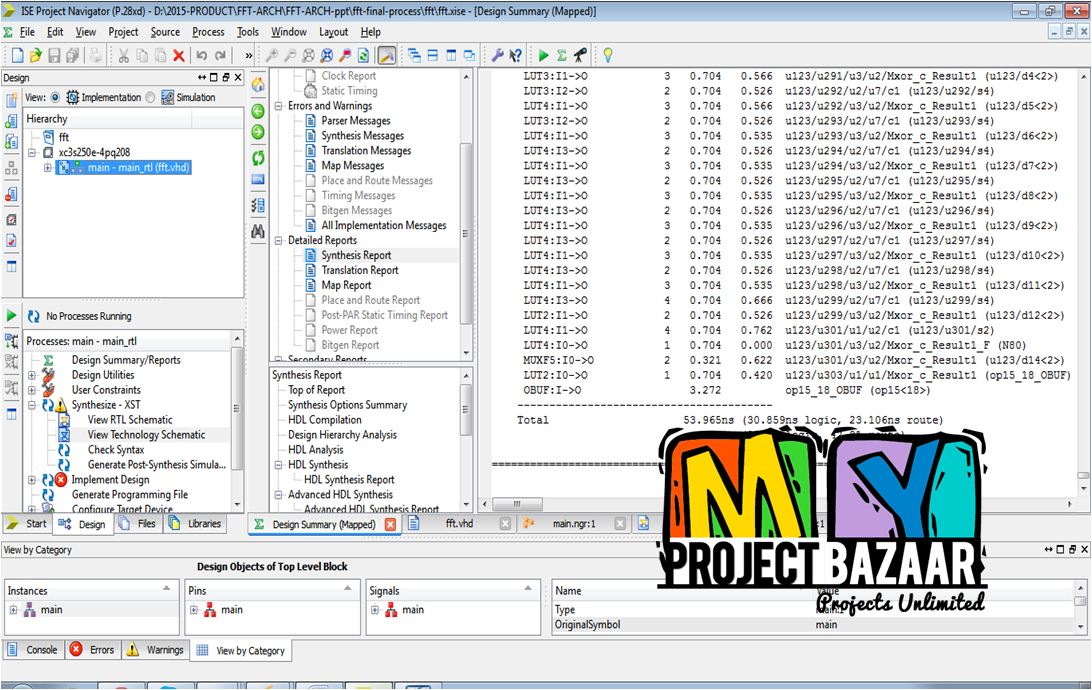

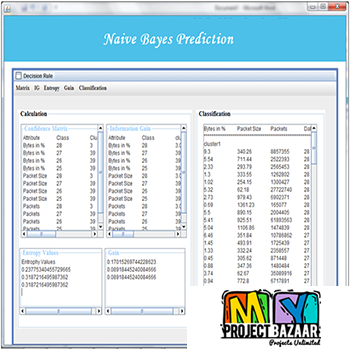

Abstract— An efficient combined single-path delay commutator-feedback < Final Year Projects 2016 > SDC-SDF radix-2 pipelined fast Fourier transform architecture, which includes log N – 1 SDC stages, and 1 SDF stage. The SDC processing engine is proposed to achieve a 100% hardware resource utilization by sharing the common arithmetic resource in the time-multiplexed approach, including both adders and multipliers. Thus, the required number of complex multipliers is reduced to log 2 N – 0.5, compared with log N – 1 for the other radix-2 SDC/SDF architectures. In addition, the proposed architecture requires roughly minimum number of complex adders log 2 N + 1 and the complex delay memory 2N + 1.5log 2 N – 1.5

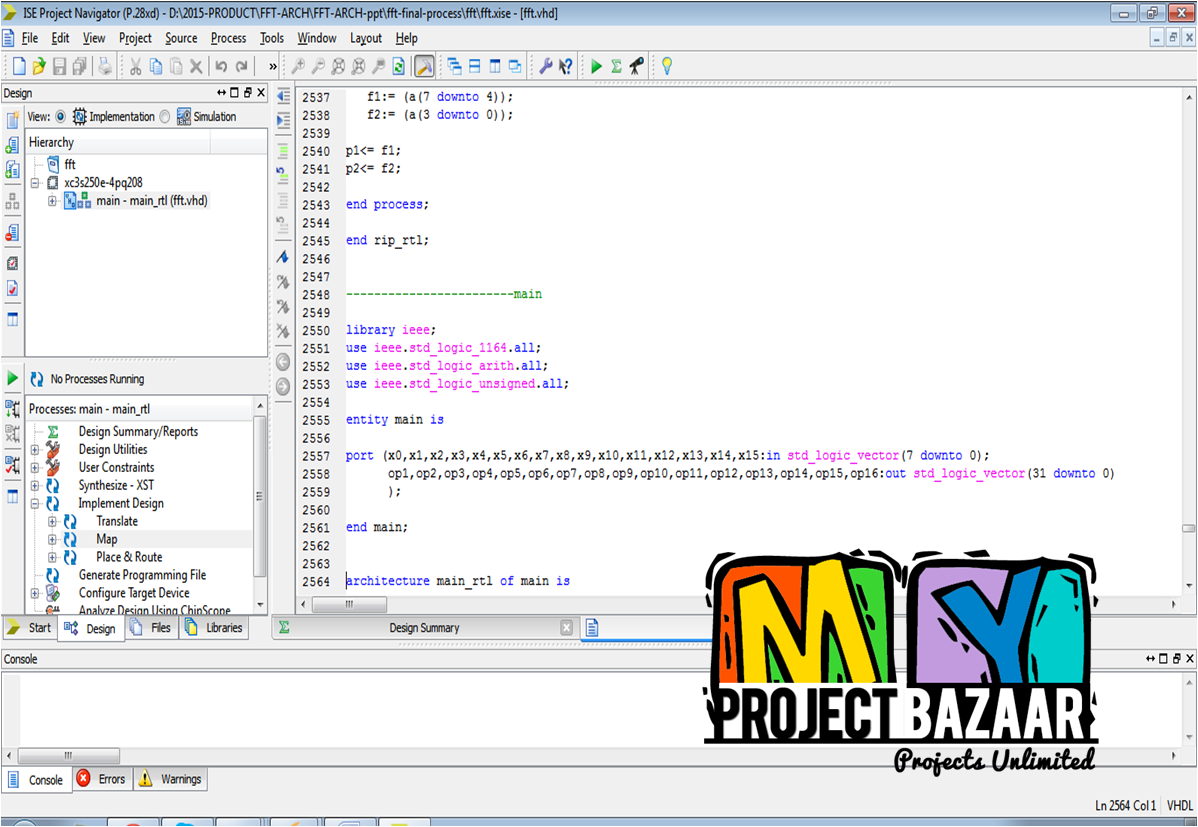

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|

Would you like to submit yours?

There are no reviews yet