A 900-MHz, 3.5-mW, 8-bit Pipelined Subranging ADC Combining Flash ADC and TDC

Product Description

A 900-MHz, 3.5-mW, 8-bit Pipelined Subranging ADC Combining Flash ADC and TDC

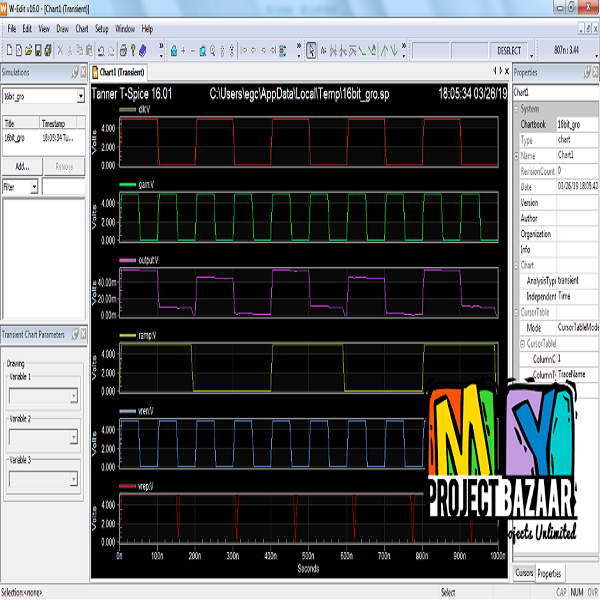

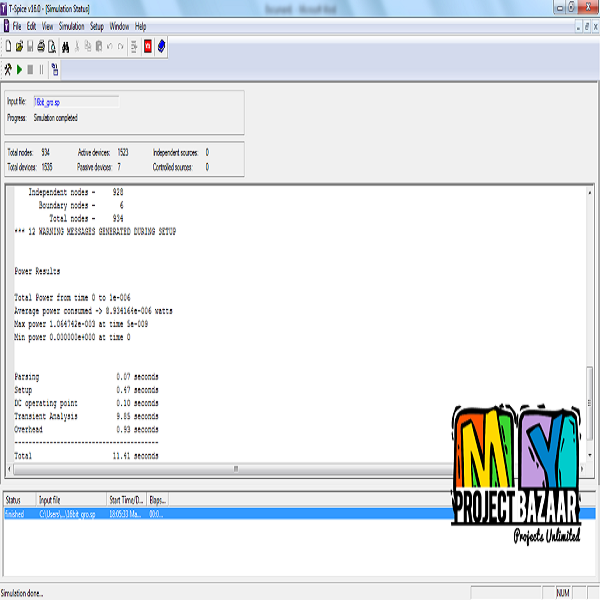

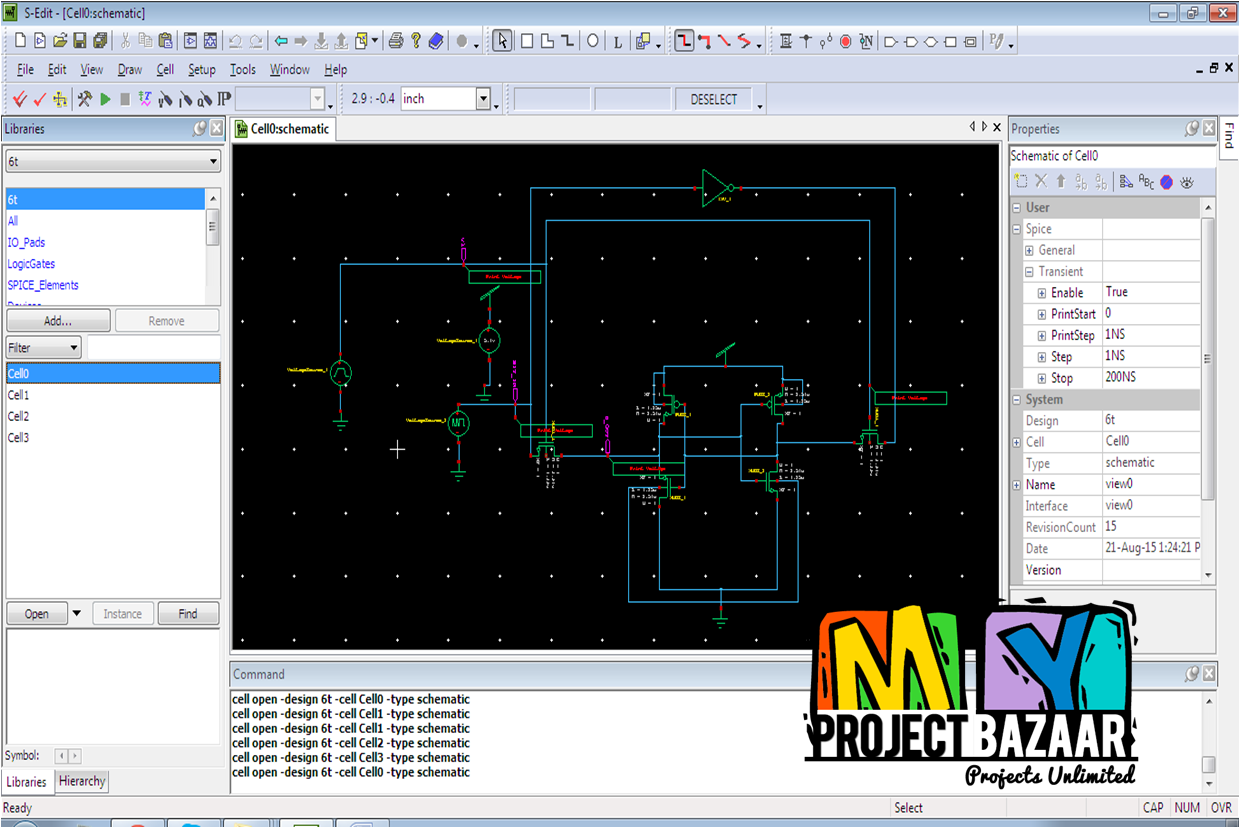

Abstract-In this paper, we propose a time-based analog-to digital converter (ADC) architecture combining a flash ADC and vernier time-to-digital converter (TDC) to achieve both high speed and high resolution. The flash ADC and vernier TDC are pipelined to increase the conversion speed. A charge-steering amplifier is used for low-power residue transfer. A common level adjuster is added to the output stage of the charge-steering amplifier to stabilize the output common level against process, voltage, and temperature variation. Moreover, the vernier TDC using a dynamic delayer enables low-power operation. An 8-bit ADC test chip fabricated with 65-nm CMOS technology had a high sampling frequency (900 MHz) and low power consumption (3.5 mW). The figure of merit was 32 fJ/conversion step.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+