A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal-Independent Delta-I Noise DfT Scheme

Product Description

A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal-Independent Delta-I Noise DfT Scheme

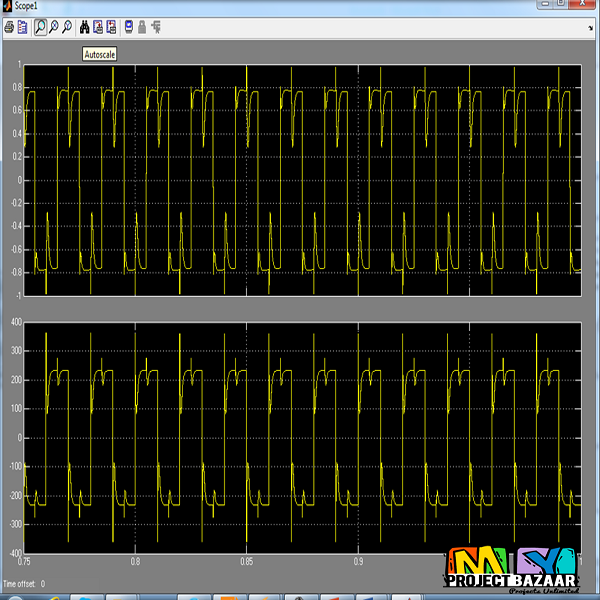

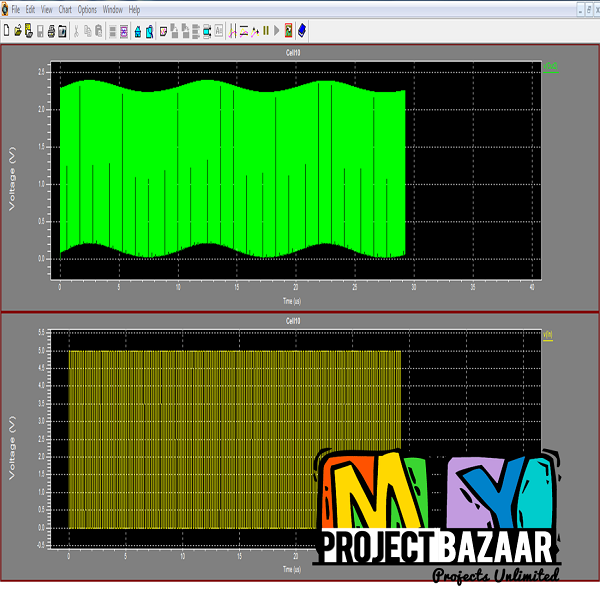

Abstract— A 28-nm CMOS 1 V 3.5 GS/s 6-bit DAC With Signal-Independent Delta-I Noise DfT Scheme. A 3.5 GS/s 6-bit current-steering digital-to-analog converter DAC with auxiliary circuitry to assist testing in a 1 V digital 28-nm CMOS process. The DAC uses only thin-oxide transistors and occupies 0.035 mm2 ,makingit suitable to embedding in VLSI systems, e.g., field-programmable gate array (FPGA).< Final Year Project 2016 > To cope with the IC process variability, a unit element approach is generally employed. The three most significant bit (MSBs) are implemented as seven unary D/A cells and the three least significant bits (LSBs) as three binary D/A cells, using appropriately reduced number of unit elements. Furthermore, all digital gates only make use of two basic unit blocks: a buffer and a multiplexer.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|

Would you like to submit yours?

There are no reviews yet