VLSI Architecture for delay efficient 32-bit Multiplier using Vedic Mathematic sutras

Product Description

VLSI Architecture for delay efficient 32-bit Multiplier using Vedic Mathematic sutras

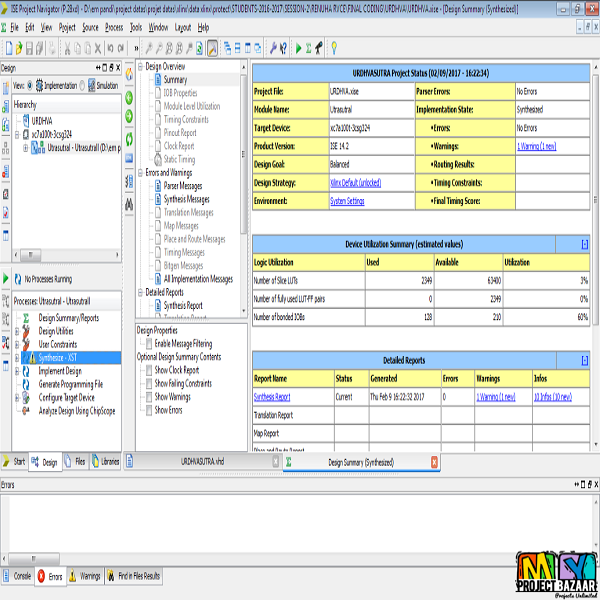

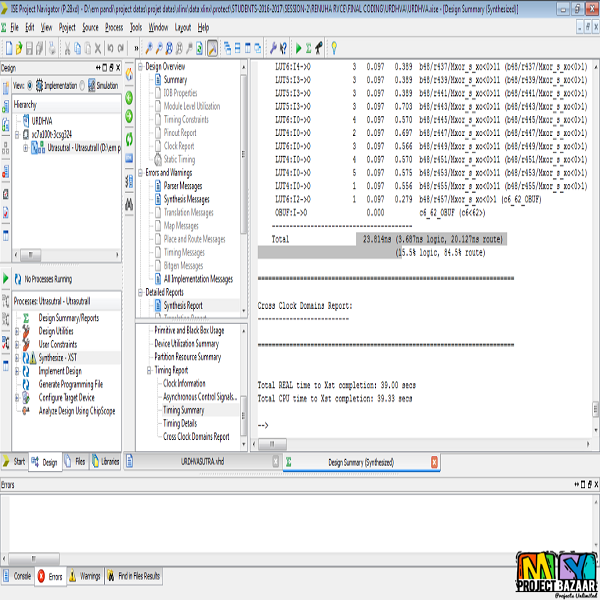

Abstract—Abstract This paper presents the VLSI Architecture for High-Speed 32-bit Multiplier using Vedic Mathematic sutras. Two sutras among 16 sutras of Vedic Mathematics can be applied for multiplication. Nikhilam Sutra and Urdhva-Tiryagbhyam Sutra are used to implement Vedic Multipliers. In this paper, VLSI architecture for both sutras is implemented and synthesized in Xilinx software. The delay and memory for multiplier using Urdhva-Tiryagbhyam sutra are less when compared to multiplier using Nikhilam sutra. Further, the structure of Vedic Multiplier is modified by using Binary to excess-1 code converter so as to obtain less delay for the multiplier. By replacing normal adders with Binary to excess-1 code converter in multipliers we can achieve reduction in delay.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+