Ultralow-Voltage High-Speed Flash ADC Design Strategy Based on FoM-Delay Product

Product Description

Ultralow-Voltage High-Speed Flash ADC Design Strategy Based on FoM-Delay Product

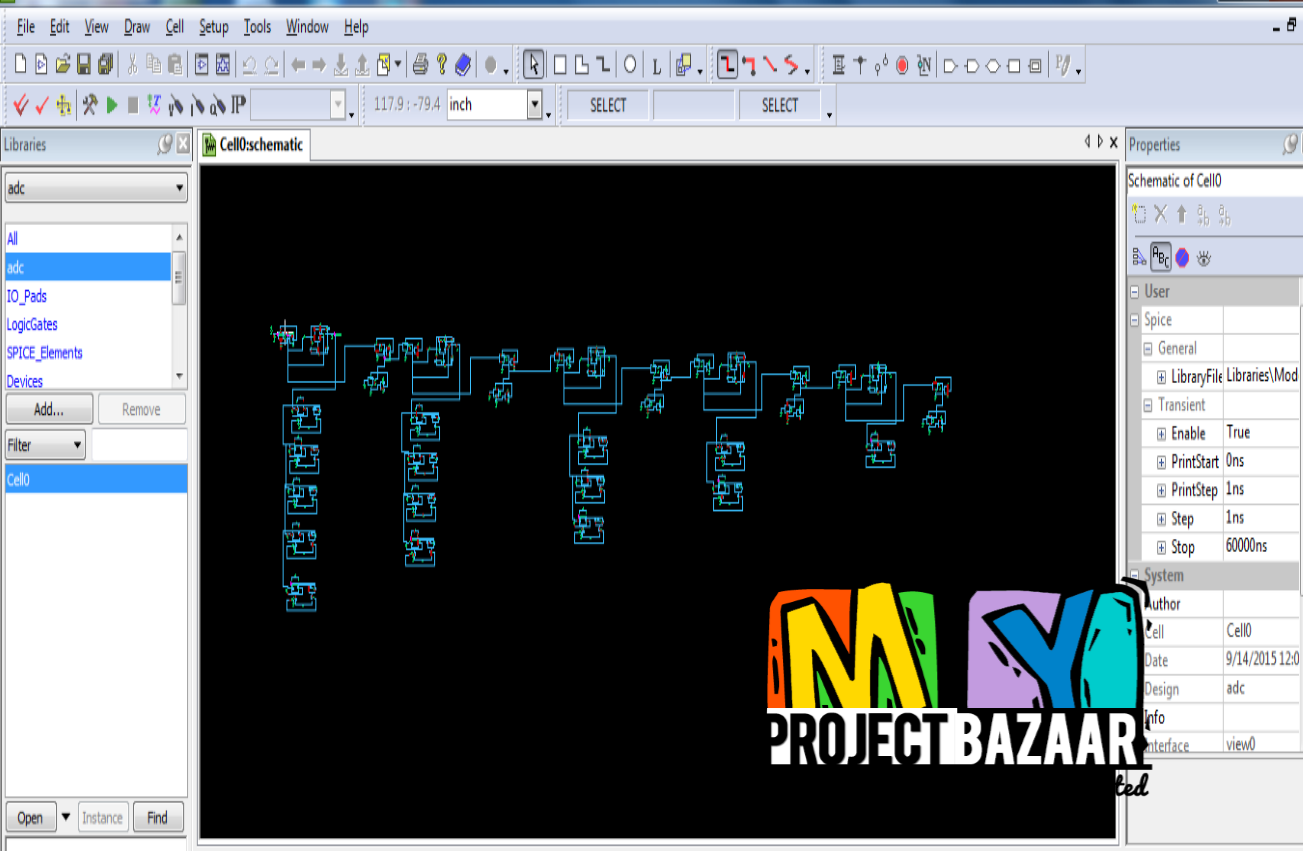

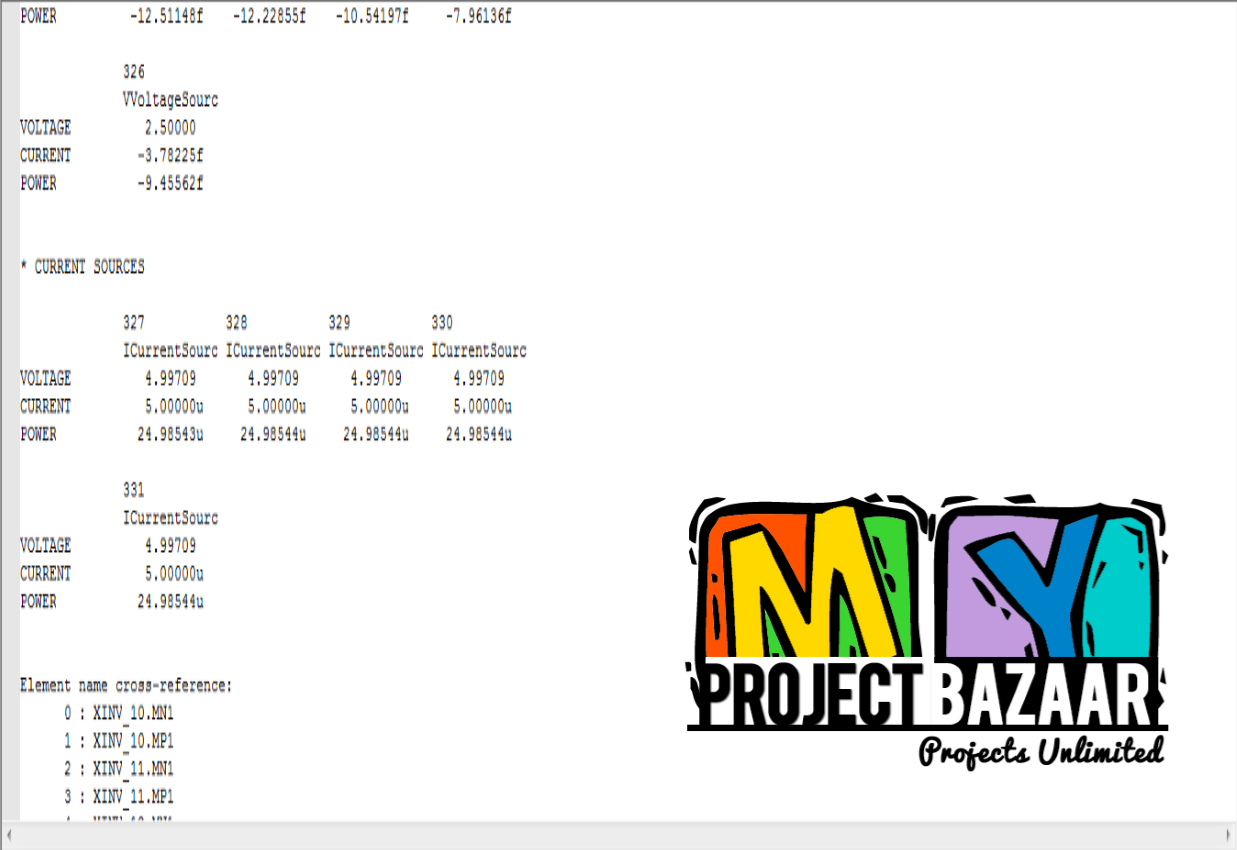

Abstract— The ultralow-voltage (ULV) design strategy for high-speed flash analog-to-digital converters (ADCs). A lower supply voltage decreases the energy consumption at the cost of conversion speed. A new index, the figure-of-merit (FoM)-delay (FD) product, is introduced to provide a balance between the energy efficiency and conversion speed. As a prototype, a 0.5 V, 420-MS/s, and 7-bit, flash ADC is developed using a 90-nm CMOS technology to demonstrate the validity of ULV operation. To overcome the challenges associated with a reduced supply voltage, a double-tail latched comparator with a variable capacitance calibration < Final Year Projects 2016 >technique using metal– oxide–metal capacitors is implemented. An all-digital time-domain delay interpolation technique further enhances the resolution with very little additional power consumption. Using two-way time-interleaving, the prototype ADC achieves an effective number of bits (ENOB) of 5.5 bits while operating at 420 MS/s consuming a total power of 4.1 mW. The lowest measured FoM is the 195 fJ/conv.-step during single-channel operation at 210 MS/s, which results in an extremely low FD product of 0.93 pJ × ns/conv.-step.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|