Trip-Point Bit-Line Precharge Sensing Scheme for Single-Ended SRAM

Product Description

Trip-Point Bit-Line Precharge Sensing Scheme for Single-Ended SRAM

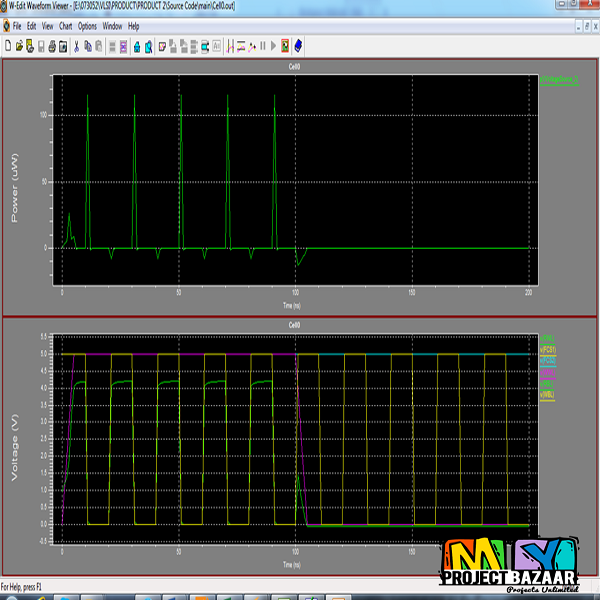

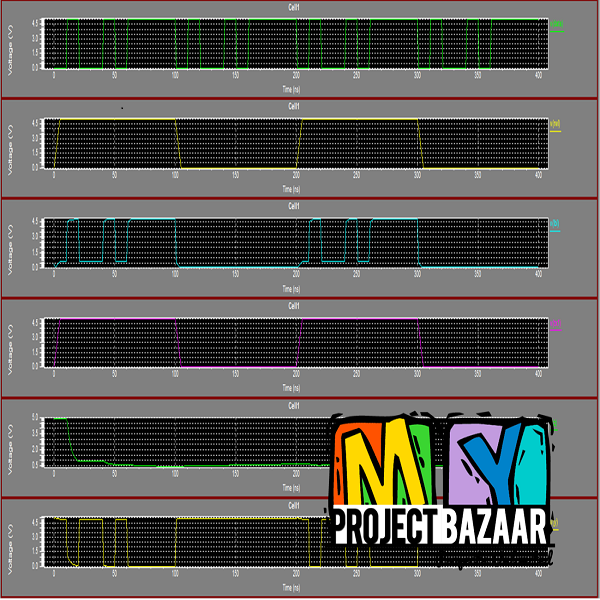

Abstract— Trip-Point Bit-Line Precharge Sensing Scheme for Single-Ended SRAM. A trip-point bit-line precharge TBP sensing scheme is proposed for high-speed single-ended static random-access memory (SRAM). < Final Year Project 2016 > This TBP scheme mitigates the issues of limited performance, power, sensing margin, and area found in the previous single-ended SRAM sensing schemes by biasing the bit-line to a slightly larger value than the trip point of the sense amplifier. Simulation results show that the TBP sensing scheme can reduce the sensing time by 58.5% and 10% compared with the domino and ac-coupled sensing schemes, respectively. Further, compared with the ac-coupled sensing scheme, the proposed scheme offers 10% lower sensing power, 36% lesser area, and a 60 mV lower value of the minimum supply voltage for the target sensing yield.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|