On System-on Chip Testing Using Hybrid Test Vector Compression

Product Description

On System-on-Chip Testing Using Hybrid Test

Vector Compression

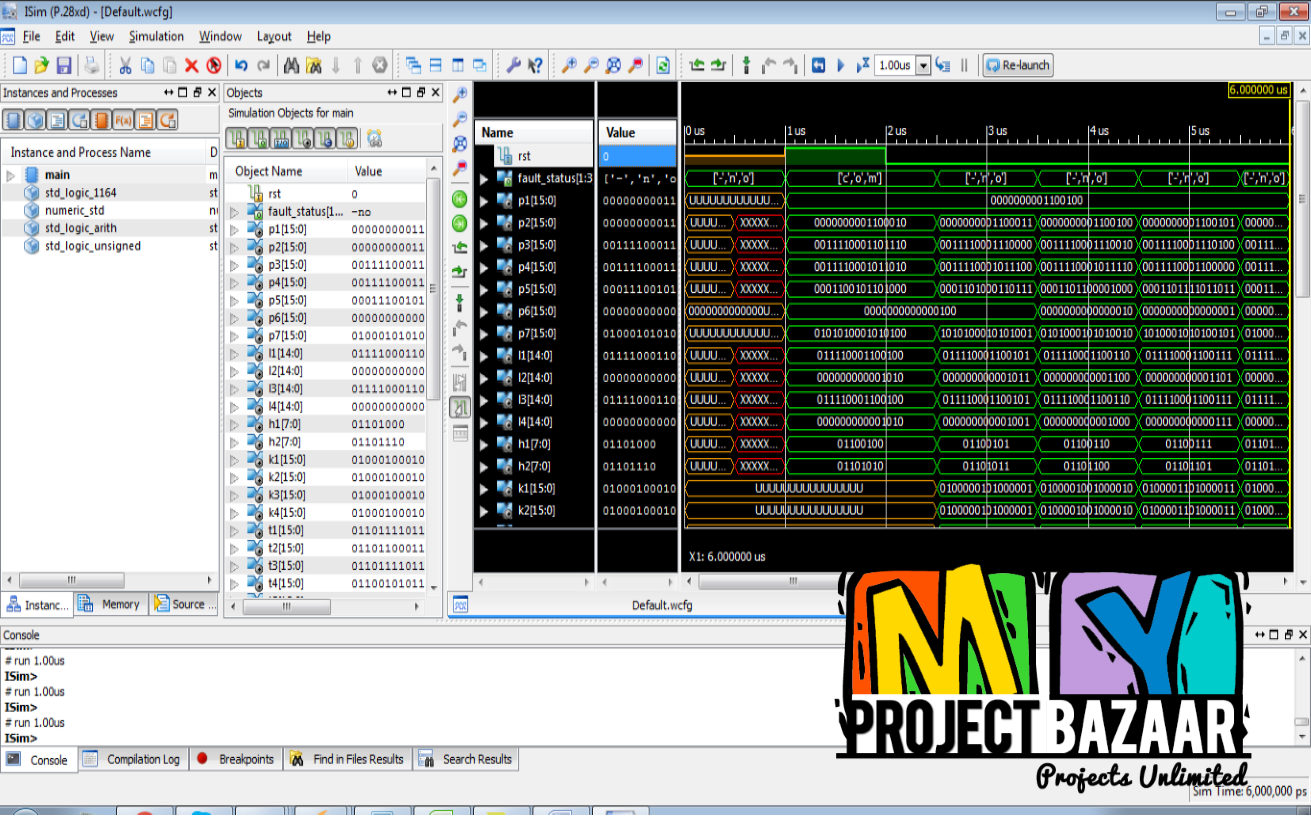

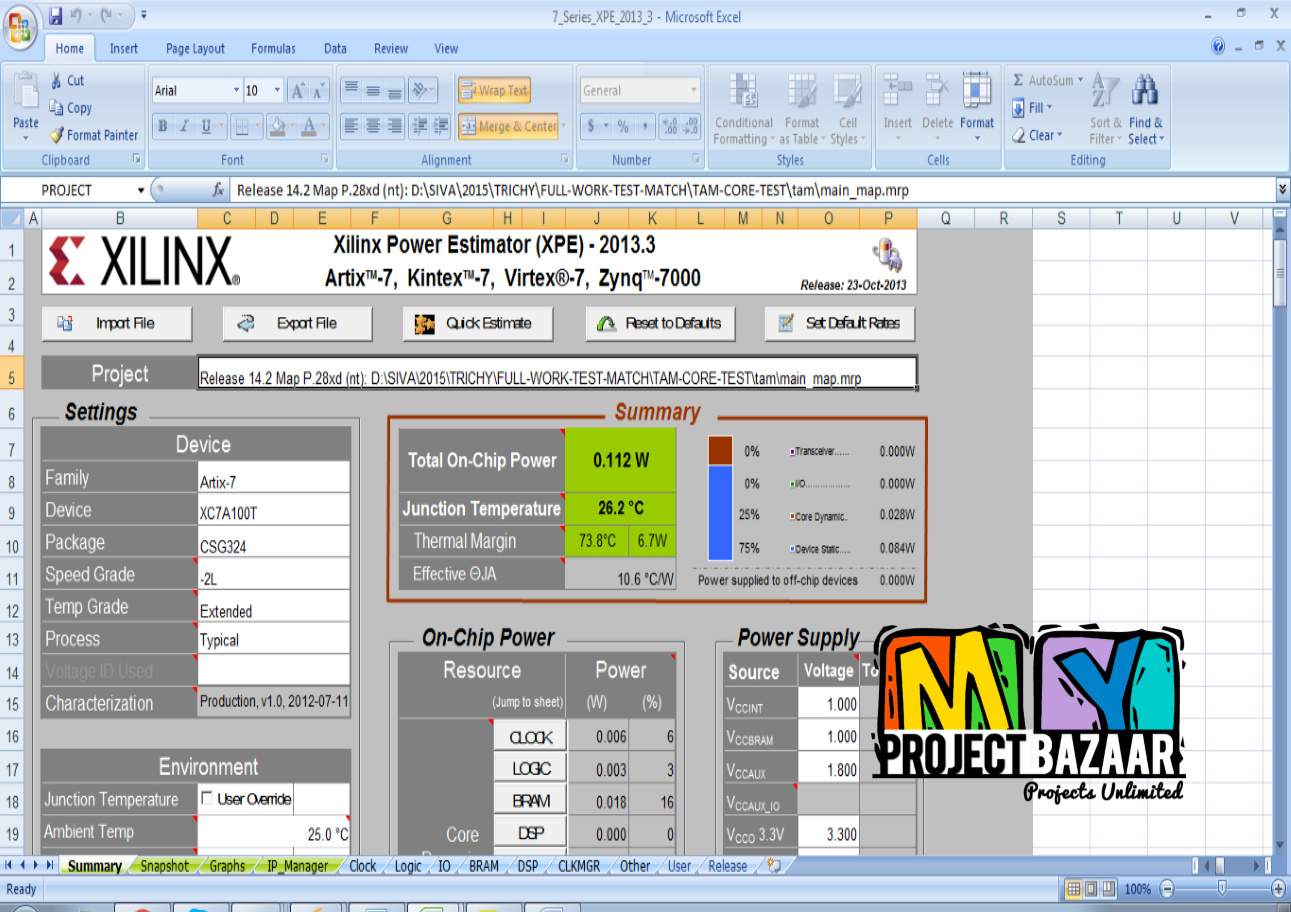

Abstract— On System-on-Chip Testing Using Hybrid Test Vector Compression. A comprehensive hybrid test vector compression method for very large scale integration (VLSI) circuit testing, targeting specifically embedded coresbased system-on-chips (SoCs). In the proposed approach, a software program is loaded into the on-chip processor memory along with the compressed test data sets. To minimize on-chip storage besides testing time, the test data volume is first reduced by compaction in a hybrid manner before downloading into the processor. The method uses a set of adaptive coding techniques for realizing lossless compression. < Final Year Projects 2016 > The compaction program need not to be loaded into the embedded processor, as only the decompression of test data is required for the automatic test equipment (ATE). The developed scheme necessitates minimal hardware overhead, while the on-chip embedded processor can be reused for normal operation on completion of testing. The reports results on studies of the problem and demonstrates the feasibility of the suggested methodology with simulation runs on the International Symposium on Circuits and Systems (ISCAS) 85 combinational and ISCAS 89 full-scan sequential benchmark circuits.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|