Sliced Message Passing: High Throughput Overlapped Decoding of High-Rate Low-Density Parity-Check Codes

Product Description

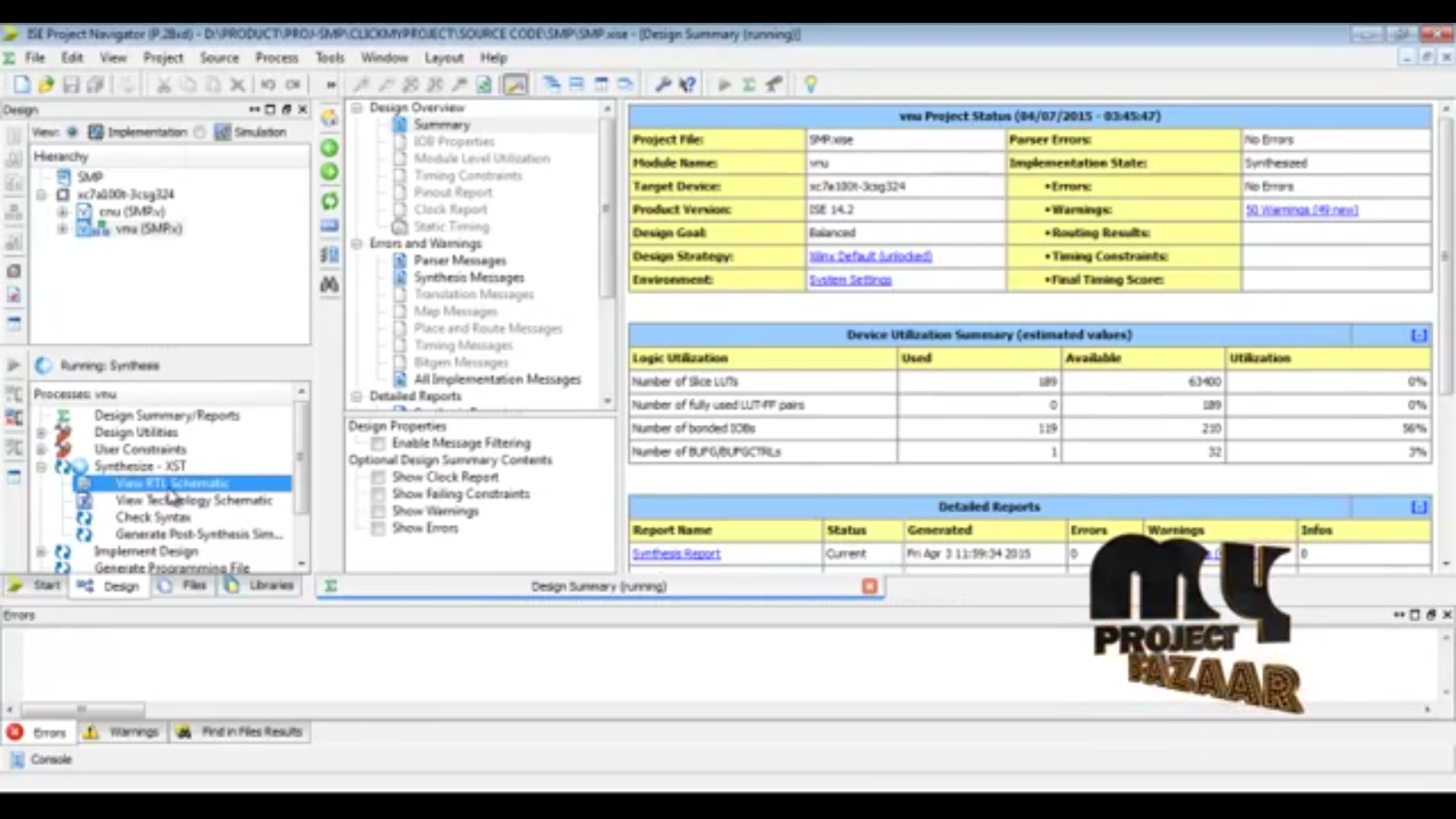

Abstract—The efficient implementation of high-rate high-throughout low-density parity-check (LDPC) code decoding presents challenges to both fully parallel decoding and memory-sharing partially parallel decoding schemes. In this paper, a new decoding scheme, sliced message passing (SMP), is introduced. The key idea is to slice the total set of N variable-to-check messages into equal-sized p chunks, < Final Year Projects > then to perform check-node computation sequentially chunk by chunk. This new decoding scheme can break the sequential tie between the check- and variable-node update stages and thus greatly improve the throughput. The hardware architectures of SMP decoding are introduced. Each check-node processing unit of the proposed register-based architecture has only c/p inputs instead of c inputs. By remapping the variable-node and check-node processing unit decoding blocks, the optimized SMP decoding units can reduce the overall hardware cost, shorten the critical-path delay, and improve the hardware-usage efficiency. An optimized SMP decoder has been further implemented for a 2048-bit (6, 32) LDPC decoder of the emerging IEEE 10 GBase-T standard in an IBM CMOS 90-nm process. Implementation results from synthesis and post layout simulation have shown the effectiveness of the proposed SMP scheme.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+