Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block

Product Description

Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block

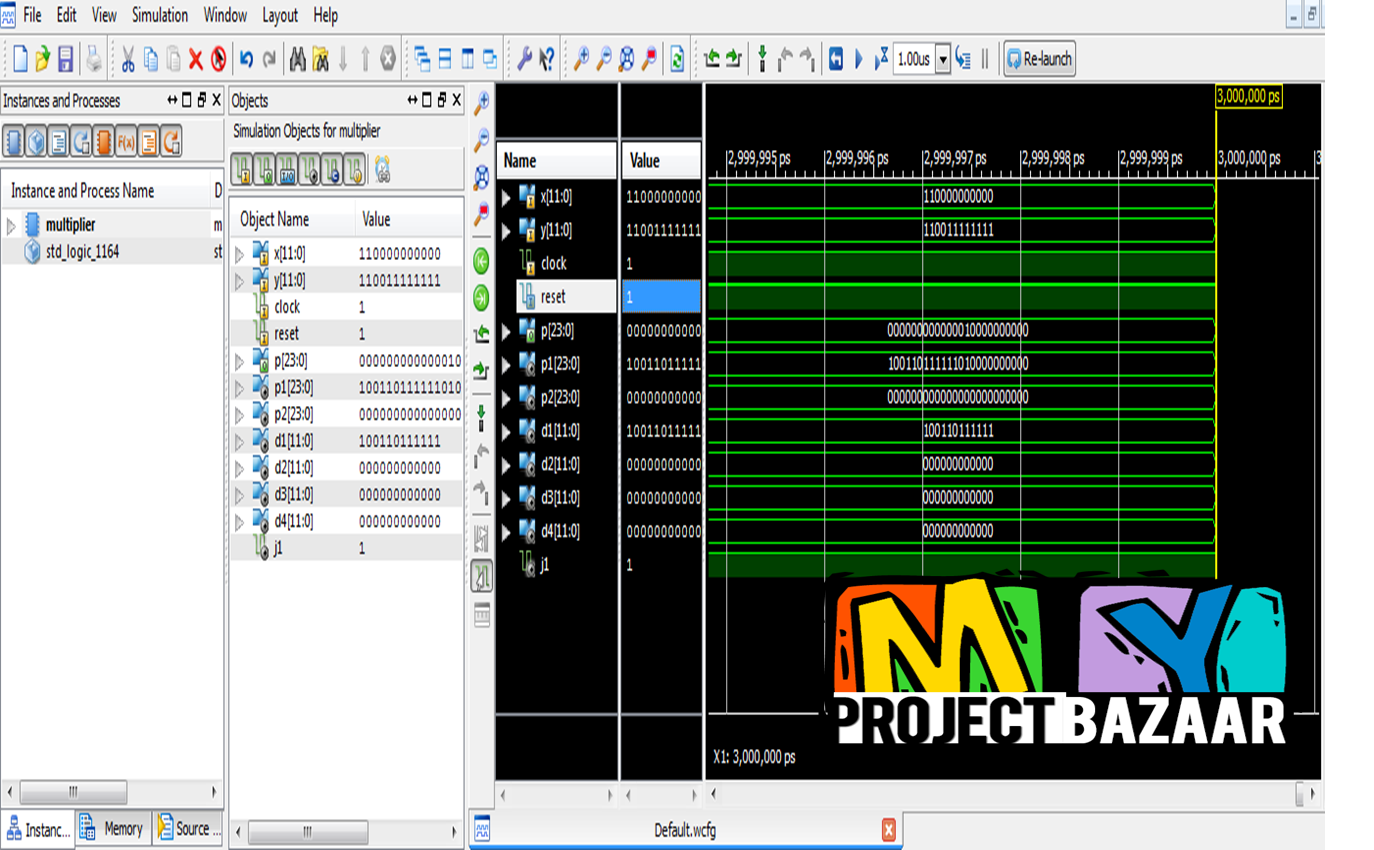

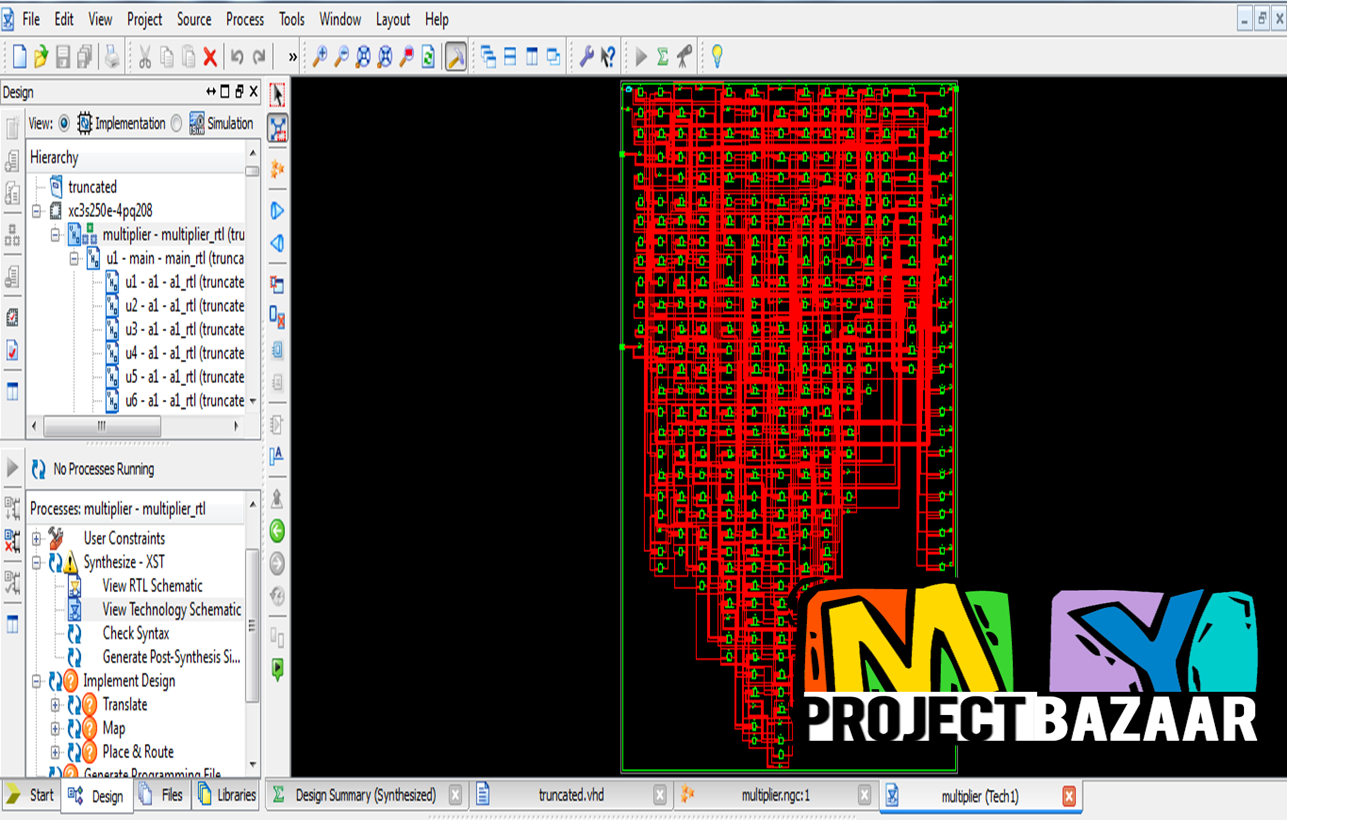

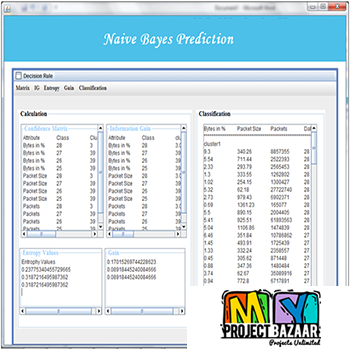

Abstract— Reliable Low-Power Multiplier Design Using Fixed-Width Replica Redundancy Block. A reliable low-power multiplier design by adopting algorithmic noise tolerant ANT architecture with the fixed-width multiplier to build the reduced precision replica redundancy block (RPR). < Final Year Project 2016 >The proposed ANT architecture can meet the demand of high precision, low power consumption, and area efficiency. We design the fixed-width RPR with error compensation circuit via analyzing of probability and statistics. Using the partial product terms of input correction vector and minor input correction vector to lower the truncation errors, the hardware complexity of error compensation circuit can be simplified. In a 12 × 12 bit ANT multiplier, circuit area in our fixed-width RPR can be lowered by 44.55% and power consumption in our ANT design can be saved by 23% as compared with the state-of-art ANT design.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|