Reducing Power, Leakage, and Area of Standard-Cell ASICs Using Threshold Logic Flip-Flops

Product Description

Reducing Power, Leakage, and Area of Standard-Cell

ASICs Using Threshold Logic Flip-Flops

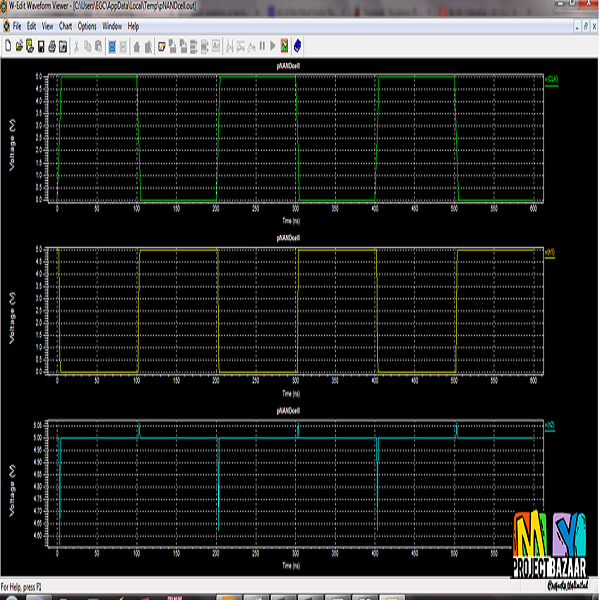

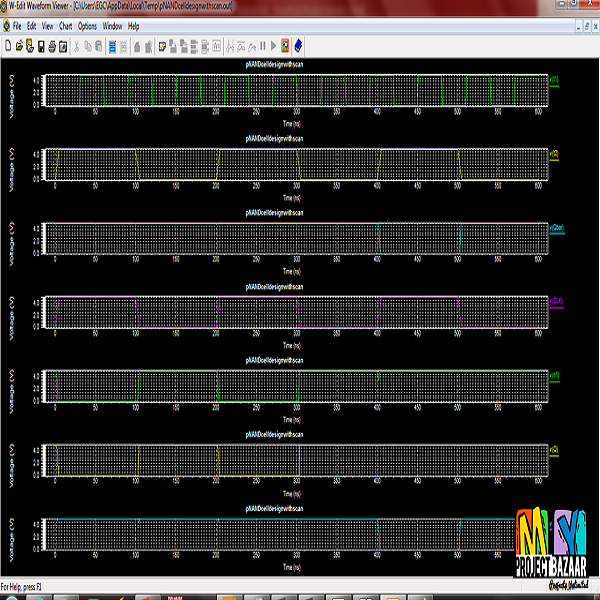

Abstract— we describe a new approach to reduce dynamic power, leakage, and area of application-specified integrated circuits, without sacrificing performance. The approach is based on a design of threshold logic gates (TLGs) and their seamless integration with conventional standard-cell design flow. We first describe a new robust, standard-cell library of configurable circuits for implementing threshold functions. Abstractly, the threshold gate behaves as a multi-input, singleoutput, edge-triggered flip-flop, which computes a threshold

function of the inputs on the clock edge. The library consists of a small number of cells, each of which can compute a set of complex threshold functions, which would otherwise require a multilevel network. The function realized by a given threshold gate is determined by how signals are mapped to its inputs.< final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+