Precise VLSI Architecture for AI Based 1-D/ 2-D Daub-6 Wavelet Filter Banks With Low Adder-Count

Product Description

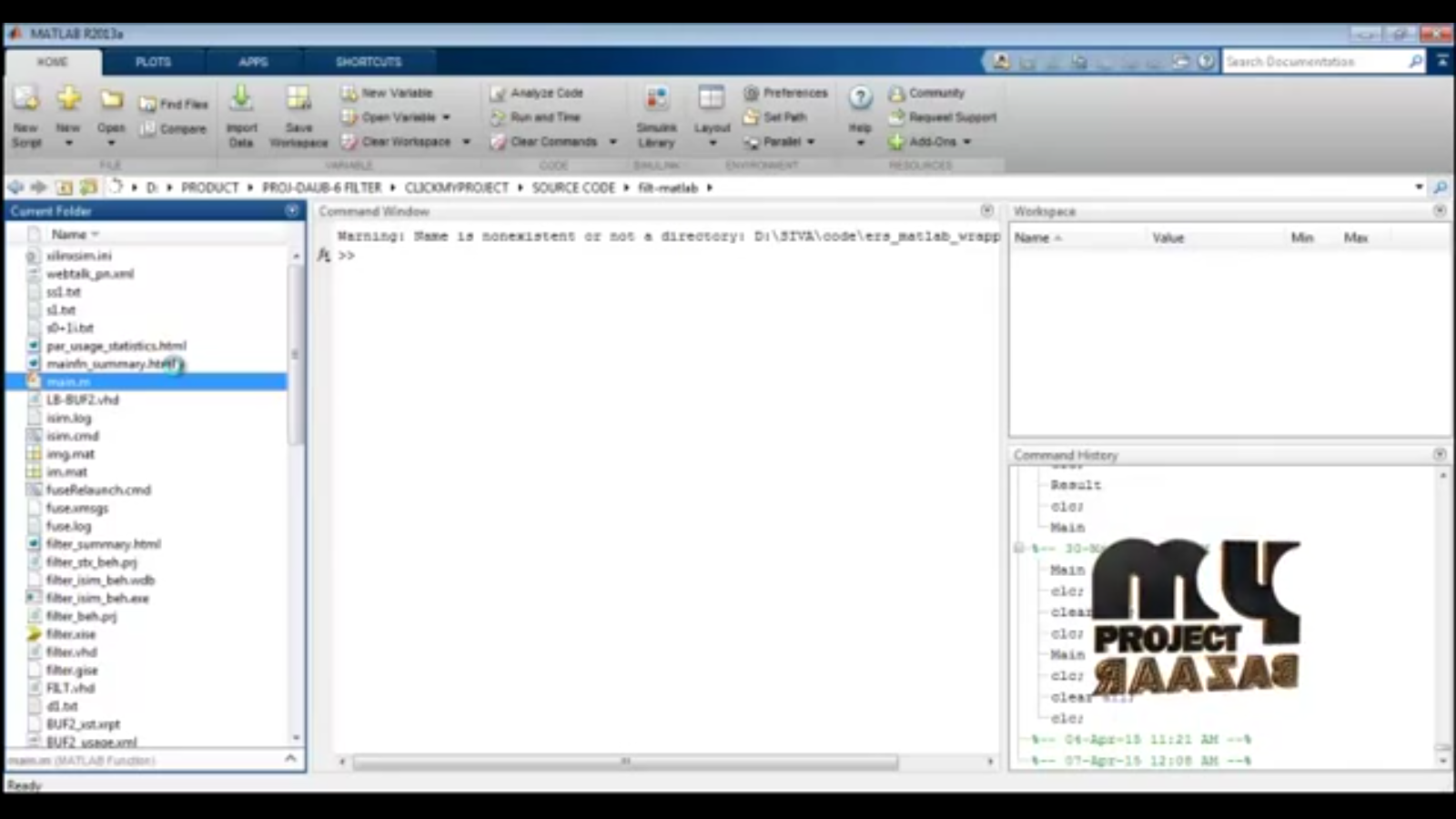

Abstract—A multiplier-less architecture based on algebraic integer representation for computing the Daubechies 6-tap wavelet transform for 1-D/2-D signal processing is proposed. This architecture improves on previous designs in a sense that it minimizes the number of parallel 2-input adder circuits. The algorithm was achieved using brute-force numerical optimization of the algebraic integer representation. The proposed architecture furnishes exact computation up to the final reconstruction step, which is the operation that maps the exactly computed filtered results from algebraic integer representation to fixed-point. Compared to our recent work, < Final Year Projects > this architecture shows a reduction of 27⋅n−16 adder circuits, where n is the number of wavelet decomposition levels. The design is physically implemented for a 4-level 1-D/2-D decomposition using a Xilinx Virtex-6 vcx240t-1ff1156 field programmable gate array (FPGA) device operating at up to a maximum clock frequency of 344/ 168 MHz. The FPGA implementation of 1-D/2-D are tested using hardware co-simulation using an ML605 board with clock of 100 MHz. A 45 nm CMOS synthesis of 2-D designs show improved clock frequency of better than 306 MHz for a supply voltage of 1.1 V.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+