Performance Analysis and Optimization for Homogenous Multi-core System based on 3D Torus Network on Chip

Product Description

Performance Analysis and Optimization for Homogenous Multi-core System based on 3D Torus Network on Chip

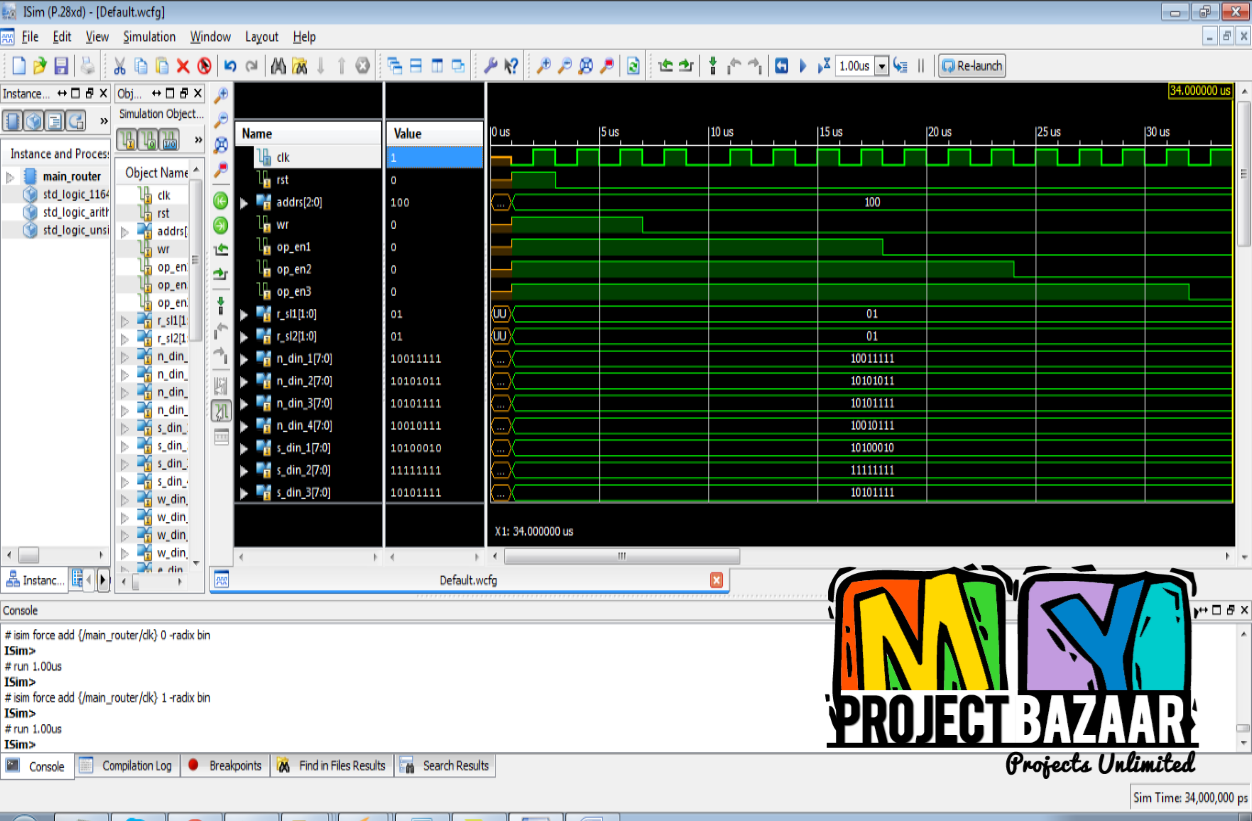

Abstract— 3D IC technology drives Network-On-Chip (NoC) design on towards 3D trend and relevant multi-core system further development. However, most recent researches still focus on the fundamental 3D Mesh structure and have no convincible traffic pattern models in realistic applications. In this paper, we present a complete design framework of a Distributed Shared Memory homogenous multi-core system based on 3D Torus interconnects. A Gray code routing mechanism is also proposed to solve deadlock. In addition, we evaluate the 3D Torus system with both Synthetic traffic uniform and transpose pattern < Final Year Projects > and real parallel multi-thread benchmark. Comparing with 3D Mesh, our experimental results demonstrate a significant reduction in the average packet latency and higher throughout put as well as a major improvement of execution cycles in typical thermal-aware IP mapping methods in 3D Torus multicore system.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|