Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit

Product Description

Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit

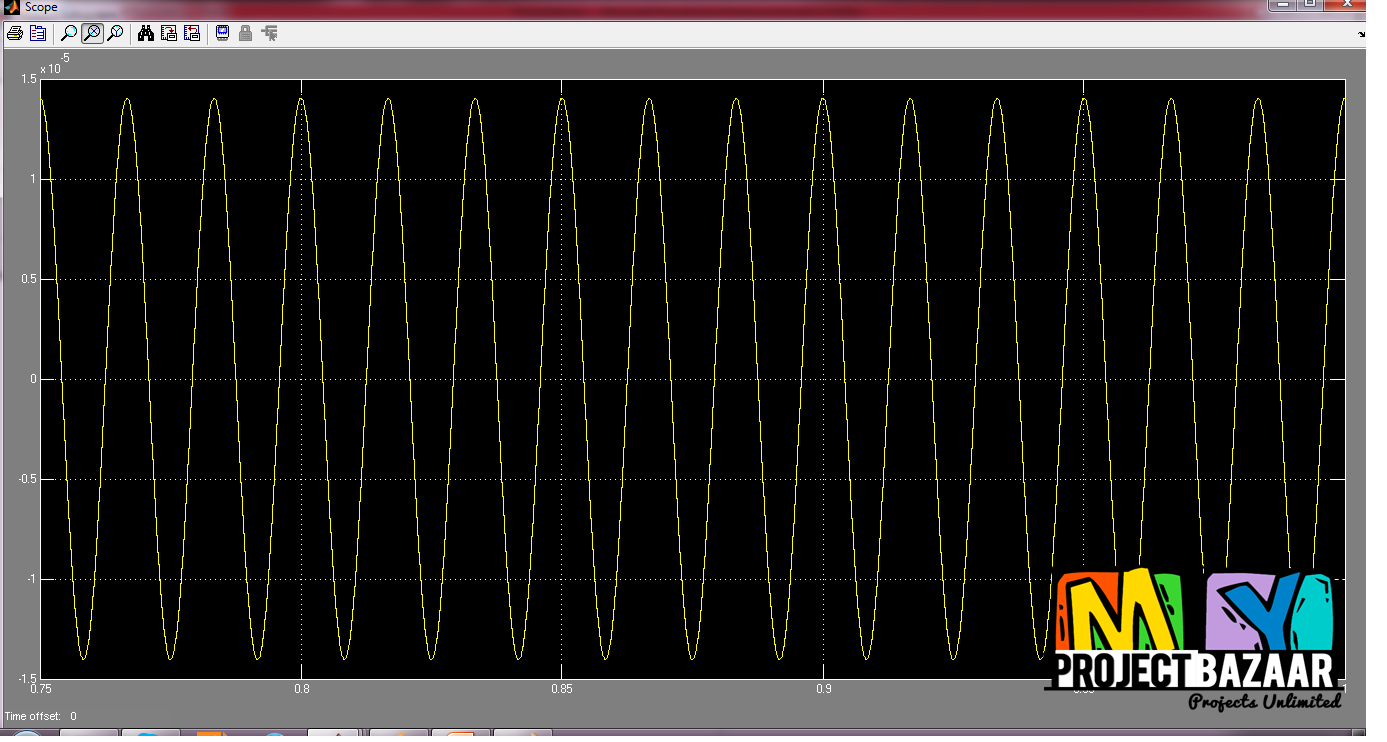

Abstract—Performance Analysis of a Low-Power High-Speed Hybrid 1-bit Full Adder Circuit. A hybrid 1-bit full adder design employing both complementary metal–oxide–semiconductor (CMOS) logic and transmission gate logic is reported.The design was first implemented for 1 bit and then extended for 32 bit also.The circuit was implemented using Cadence Virtuoso tools in 180-and 90-nm technology. Performance parameters such as power, delay, and layout area were compared with the existing designs such as complementary pass-transistor logic, transmission gate adder, transmission function adder, hybrid pass-logic with static CMOS output drive full adder, and so on. For 1.8-V supply at 180-nm technology, the average power consumption (4.1563 µW) was found to be extremely low with moderately low delay < Final Year Projects 2016 > 224 ps > resulting from the deliberate incorporation of very weak CMOS inverters coupled with strong transmission gates.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains | |

|---|---|

| Programming Language |