Partial Access Mode: New Method for Reducing Power Consumption of Dynamic Random Access Memory

Product Description

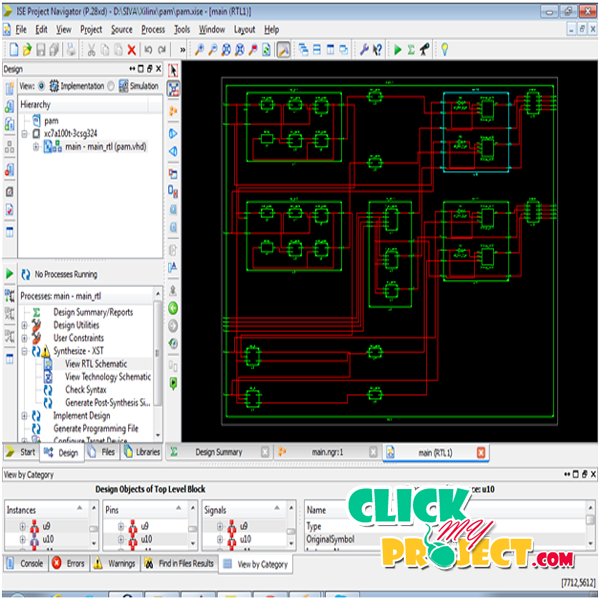

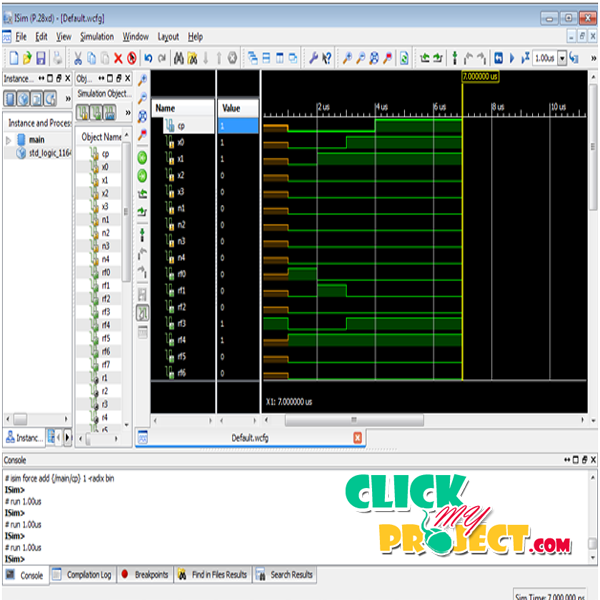

Power Consumption of Dynamic Random Access Memory”

Abstract—Partial Access Mode: New Method for Reducing Power Consumption of Dynamic Random Access Memory. Demands have been placed on a dynamic random access memory (DRAM) to not only have increased memory capacity and data transfer speed, but also have reduced operating and standby currents. When a system uses a DRAM, a refresh operation is necessary because of its data retention time restriction: each bit of the DRAM is stored as an amount of electrical charge in a storage capacitor that is discharged by the leakage current. Power consumption for the refresh operation increases in proportion to the memory capacity. We propose a new method to reduce the refresh power consumption by effectively extending the memory cell retention time. Conversion from 1 cell/bit to 2N cells/bit reduces the variation in the retention time among memory cells. Although active power increases by a factor of 2N, < Final Year Projects > the refresh time increases by more than 2N as a consequence of the fact that the majority decision does better than averaging for the tail distribution of retention time. The conversion can be realized very simply from the structure of the DRAM array circuit, and it reduces the frequency of disturbance and power consumption by two orders of magnitude. On the basis of this conversion method, we propose a partial access mode to reduce power consumption dynamically when the full memory capacity is not required.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+