Parasitics-Aware Design of Symmetric and Asymmetric Gate-Workfunction FinFET SRAMs

Product Description

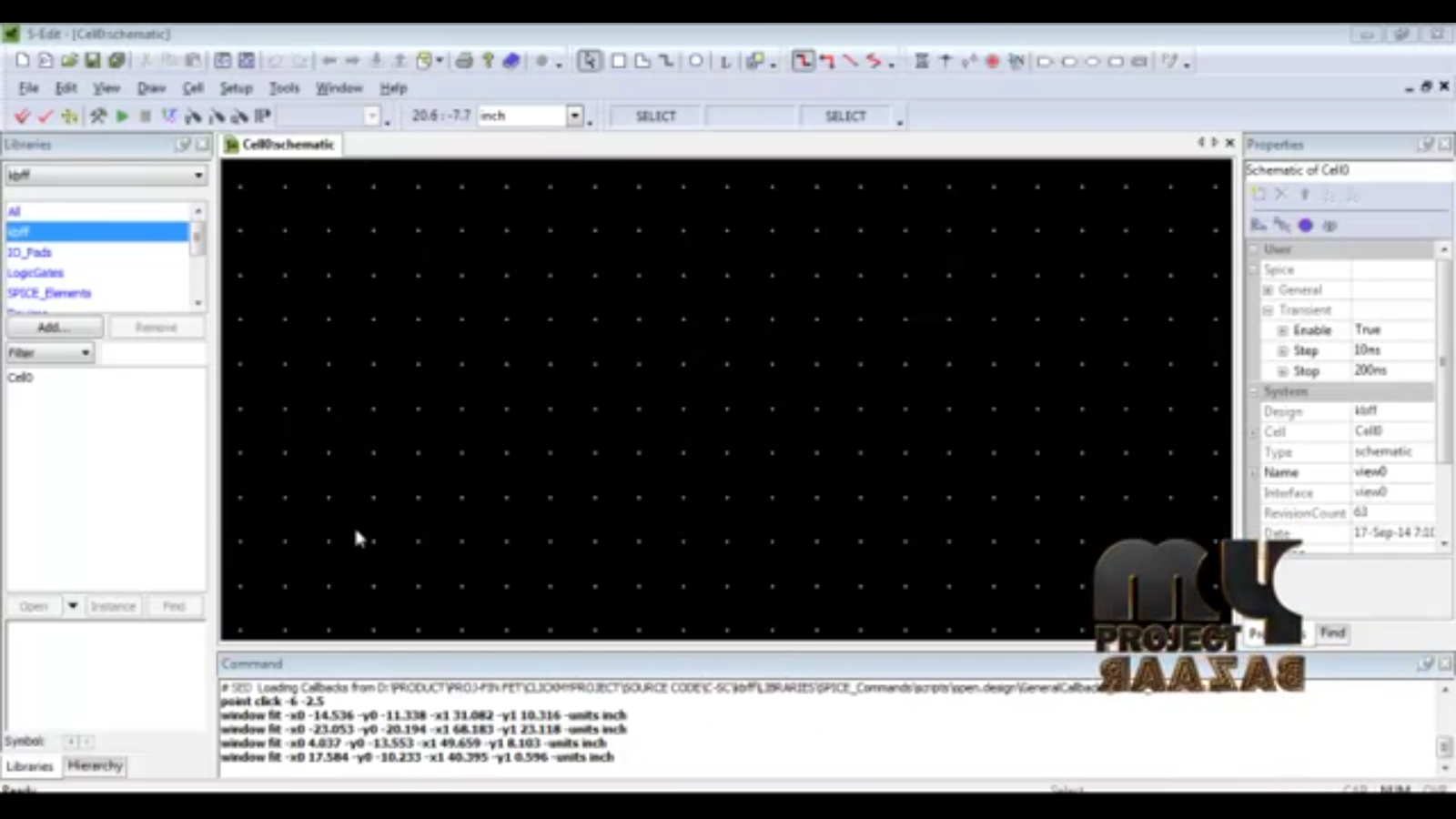

Abstract— Multigate FET technology is the most viable successor to planar CMOS technology at the 22-nm node and beyond. Prior research on multigate SRAMs is generally confined to the optimization of DC targets. However, on account of the nonplanar nature of multigate FETs,< Final Year Projects > it is highly questionable whether multigate SRAM DC metrics can guide bitcell designers, as parasitic capacitances for two topologically equivalent bitcells can be very different – due to various issues such as fin pitches – resulting in widely varying transient characteristics. In this paper, we evaluate several known symmetric gate-workfunction (Symm- ΦG) 6T FinFET SRAMs and, for the first time, asymmetric gate-workfunction (Asymm-ΦG) 6T FinFET SRAMs, head-to-head in a 22-nm silicon-on-insulator process, from the perspective of transient behavior, using a unified 3-D/mixed-mode 2-D TCAD technology-circuit co-design methodology. We accomplish the latter by capturing bitcell parasitics accurately through transport analysis-based 3-D TCAD capacitance extractions that leverage automated layout-3-D TCAD structure synthesis algorithms. Mixed-mode transient device simulations (incorporating back-annotated 3-D TCAD parasitics) indicate that a design guided by DC metrics alone can lead to erroneous conclusions and suboptimal bitcell choices. Overall, from the perspective of area and performance, in single- ΦG processes, shorted-gate (or vanilla) configurations are superior to topologies employing independent-gate configurations, even though the latter often have better DC metrics. In a larger design space encompassing dual/Asymm-ΦG devices, Asymm-ΦG FinFET SRAMs are very competitive with respect to vanilla topologies in terms of DC metrics and have better dynamic write-ability, even at low VDD.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+