A Parallel Digital VLSI Architecture for Integrated Support Vector Machine Training and Classification

Product Description

A Parallel Digital VLSI Architecture for Integrated Support Vector Machine Training and Classification

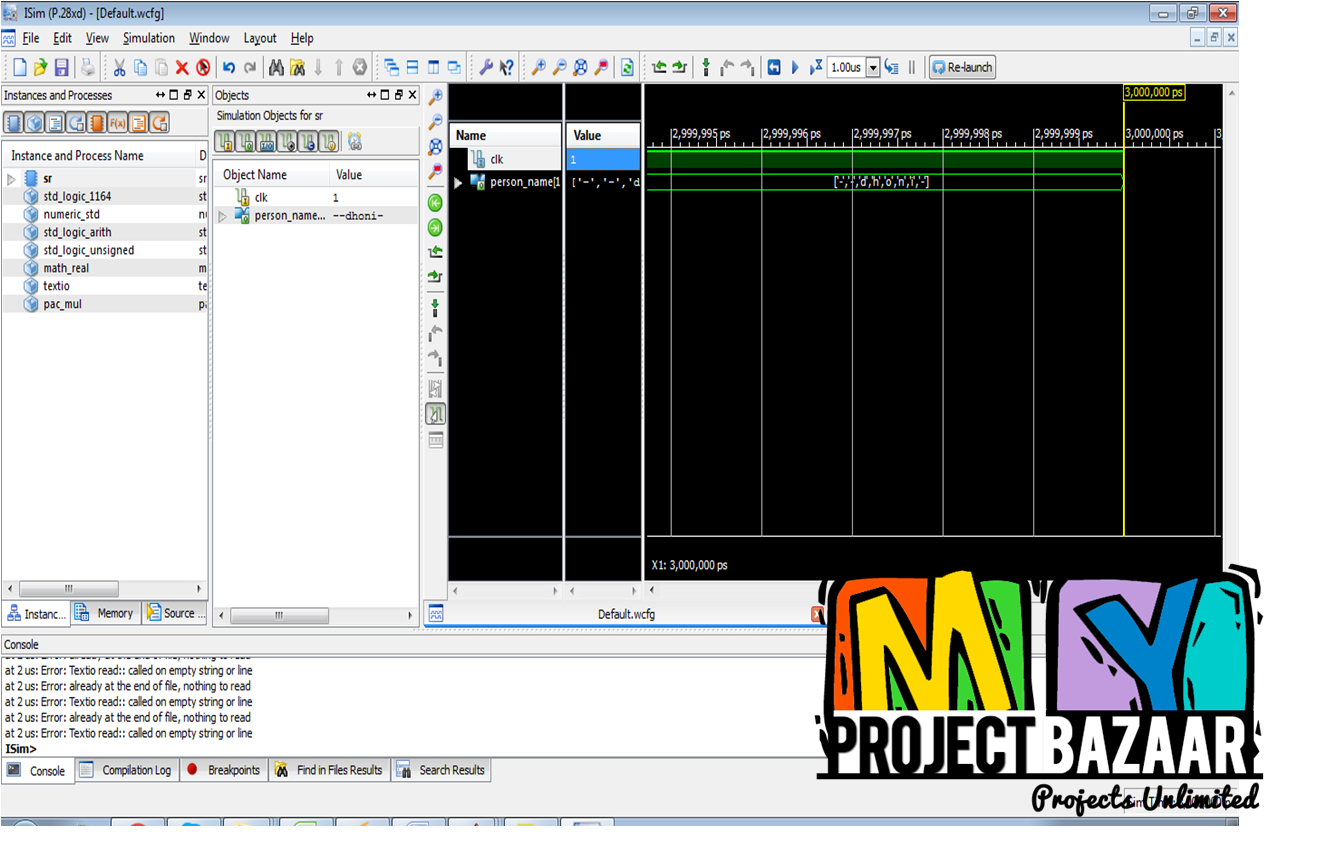

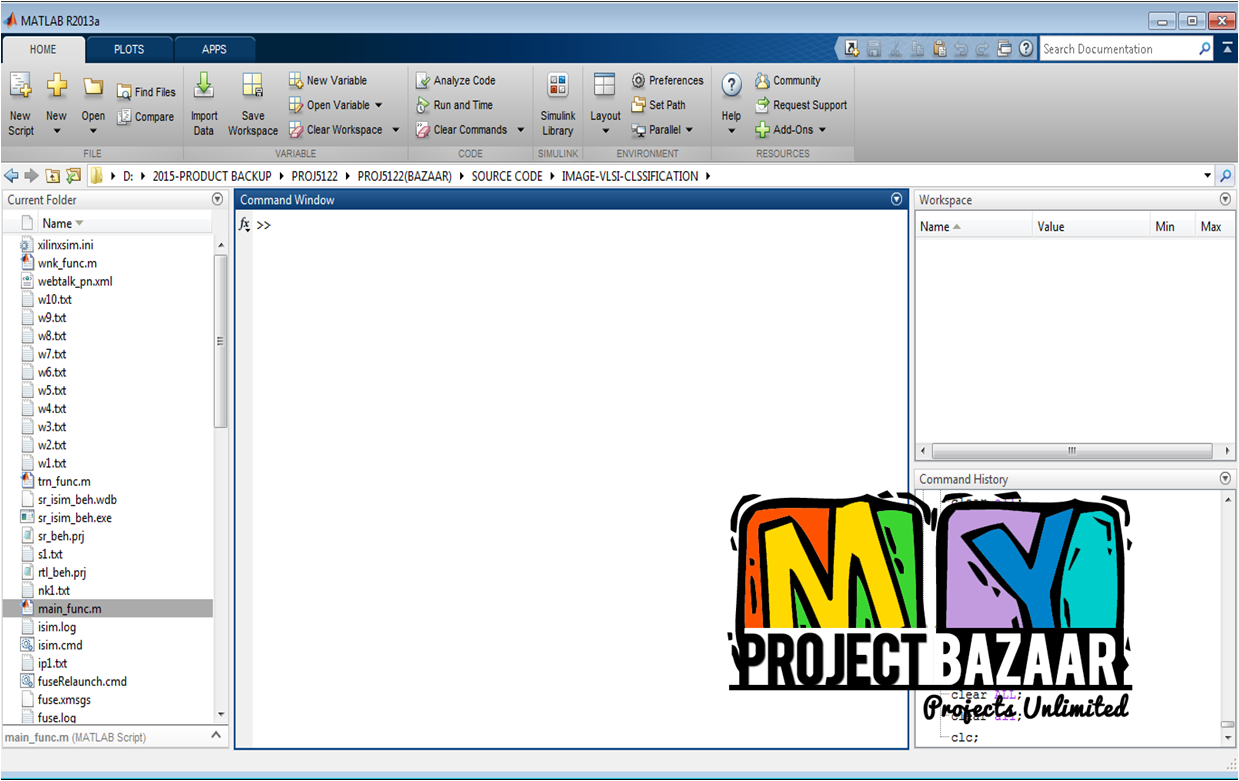

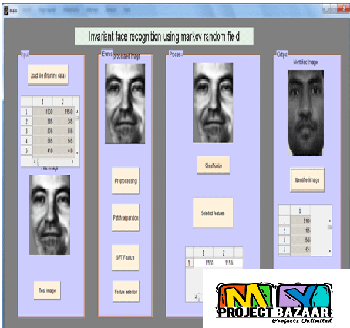

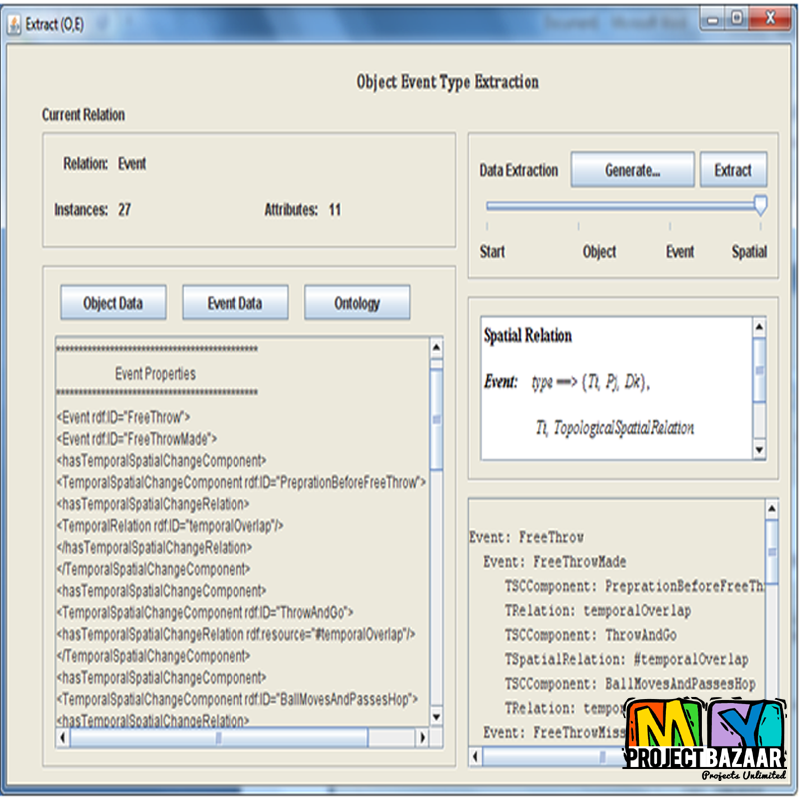

Abstract—A parallel digital VLSI architecture for combined support vector machine < Final Year Projects 2016 > SVM training and classification. For the first time, cascade SVM, a powerful training algorithm, is leveraged to significantly improve the scalability of hardware-based SVM training and develop an efficient parallel VLSI architecture. The presented architecture achieves excellent scalability by spreading the training workload of a given data set over multiple SVM processing units with minimal communication overhead. Hardware-friendly implementation of the cascade algorithm is employed to achieve low hardware overhead and allow for training over data sets of variable size.In the proposed parallel cascade architecture, a multilayer system bus and multiple distributed memories are used to fully exploit parallelism.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|