A Novel VLSI DHT Algorithm for a Highly Modular and Parallel Architecture

Product Description

Abstract—A new very large scale integration (VLSI) algorithm for a 2N-length discrete Hartley transform (DHT) that can be efficiently implemented on a highly modular and parallel VLSI architecture having a regular structure is presented. The DHT algorithm can be efficiently split on several parallel parts that can be executed concurrently. Moreover, the proposed algorithm is well suited for the subexpression sharing technique that can be used to significantly reduce the hardware complexity of the highly parallel VLSI implementation. Using the advantages of the proposed algorithm and the fact that we can efficiently share the multipliers with the same constant, the number of the multipliers has been significantly reduced such that the number of multipliers is very small comparing with that of the existing algorithms. Moreover, < Final Year Projects > the multipliers with a constant can be efficiently implemented in VLSI.

Including Packages

Our Specialization

Support Service

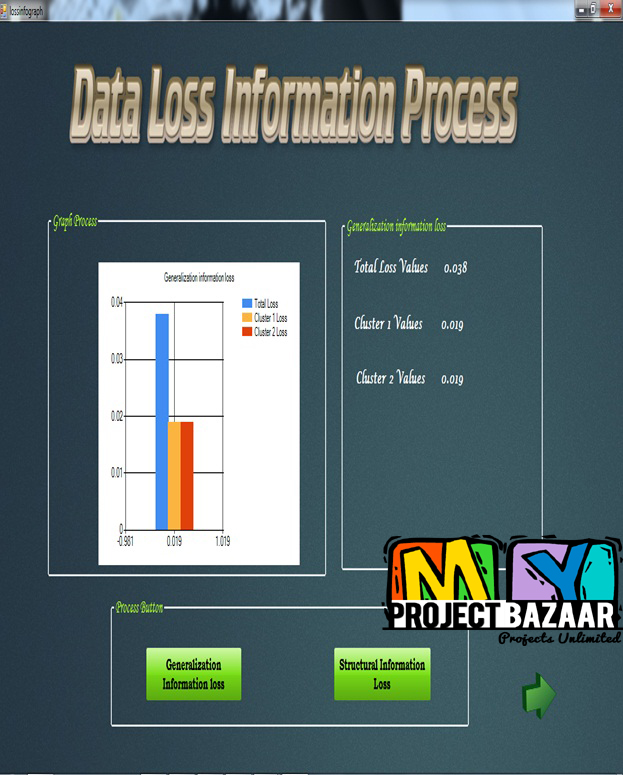

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+