A Novel Two-Split Capacitor Array with Linearity Analysis for High-Resolution SAR ADCs

Product Description

A Novel Two-Split Capacitor Array with

Linearity Analysis for High-Resolution SAR

ADCs

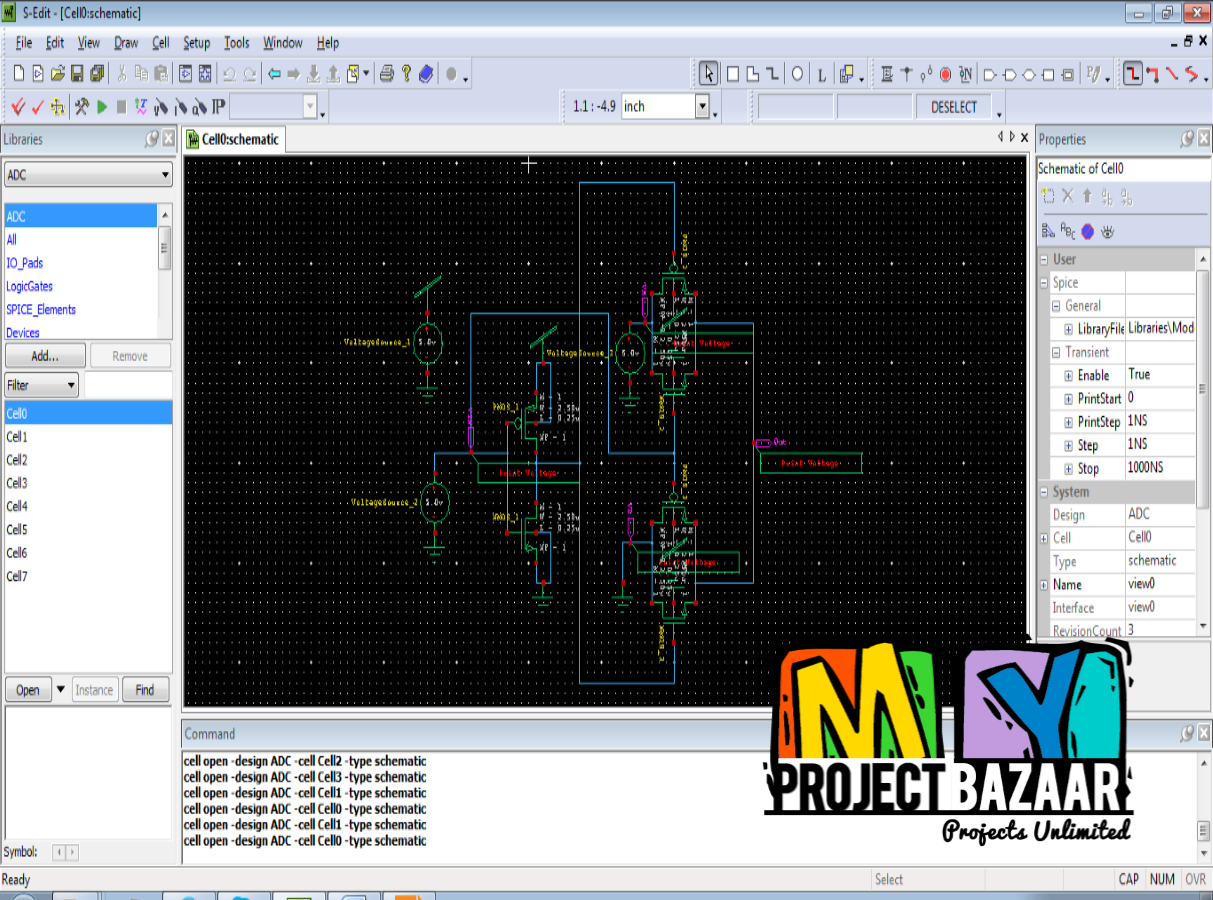

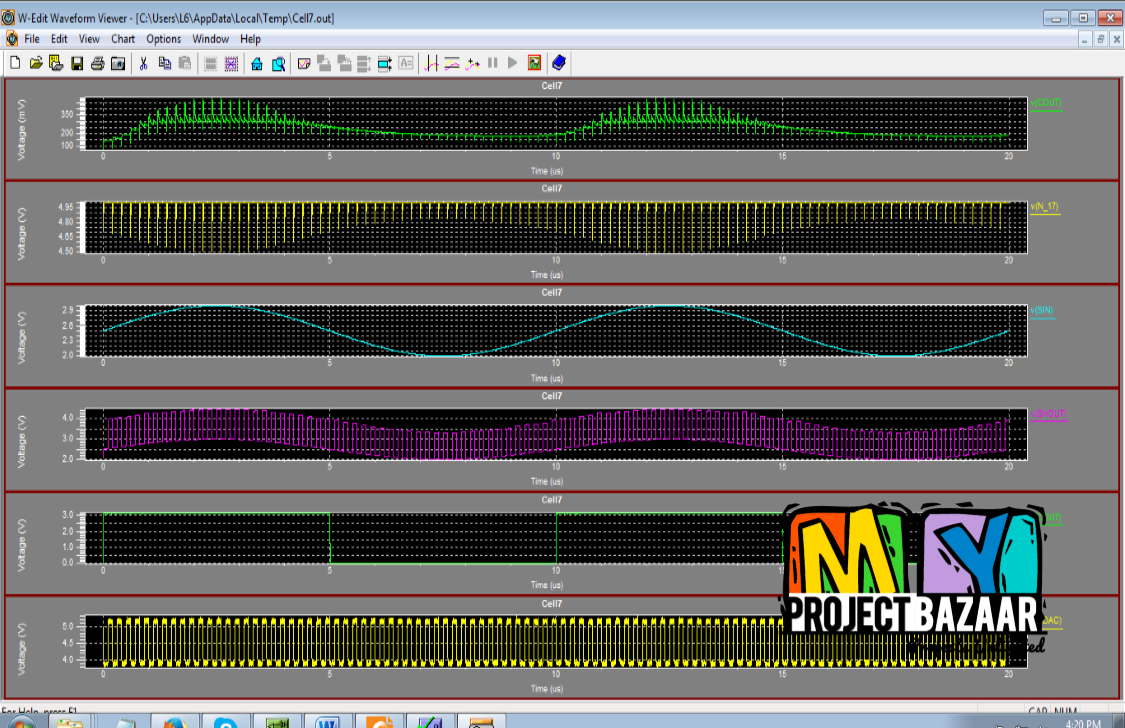

Abstract— A Novel Two-Split Capacitor Array with Linearity Analysis for High-Resolution SAR ADCs. A novel two-split capacitor < Final Year Projects 2016 > T-SC array structure for Successive Approximation Register (SAR) analog-to-digital converter (ADC) is proposed. When used as digital –to-analog converter (DAC), this circuit reduced the chip area by 27.7% in comparing with the conventional Split Capacitor (SC) at resolution=14. The area reduction effect can be more significant with the increasing resolution of ADC. The capacitor mismatch and parasitic effects of this proposed structure are analyzed in theory. Behavioral simulations were performed to demonstrate the effectiveness of this proposed structure. This simulation was only performed for capacitor mismatch. Simulation results show that T-SC array could achieve good binary-weighted performance and the standard deviation of its DNL was 0.51LSB when the standard deviation of capacitor was 0.025%. Furthermore, the analysis in this paper is provided for designers to make a tradeoff among resolution, CMOS process, circuit structure and capacitor size in their design of SAR ADC.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|