An 8T Low-Voltage and Low-Leakage Half-Selection Disturb-Free SRAM Using Bulk-CMOS and FinFETs

Product Description

An 8T Low-Voltage and Low-Leakage

Half-Selection Disturb-Free SRAM Using

Bulk-CMOS and FinFETs

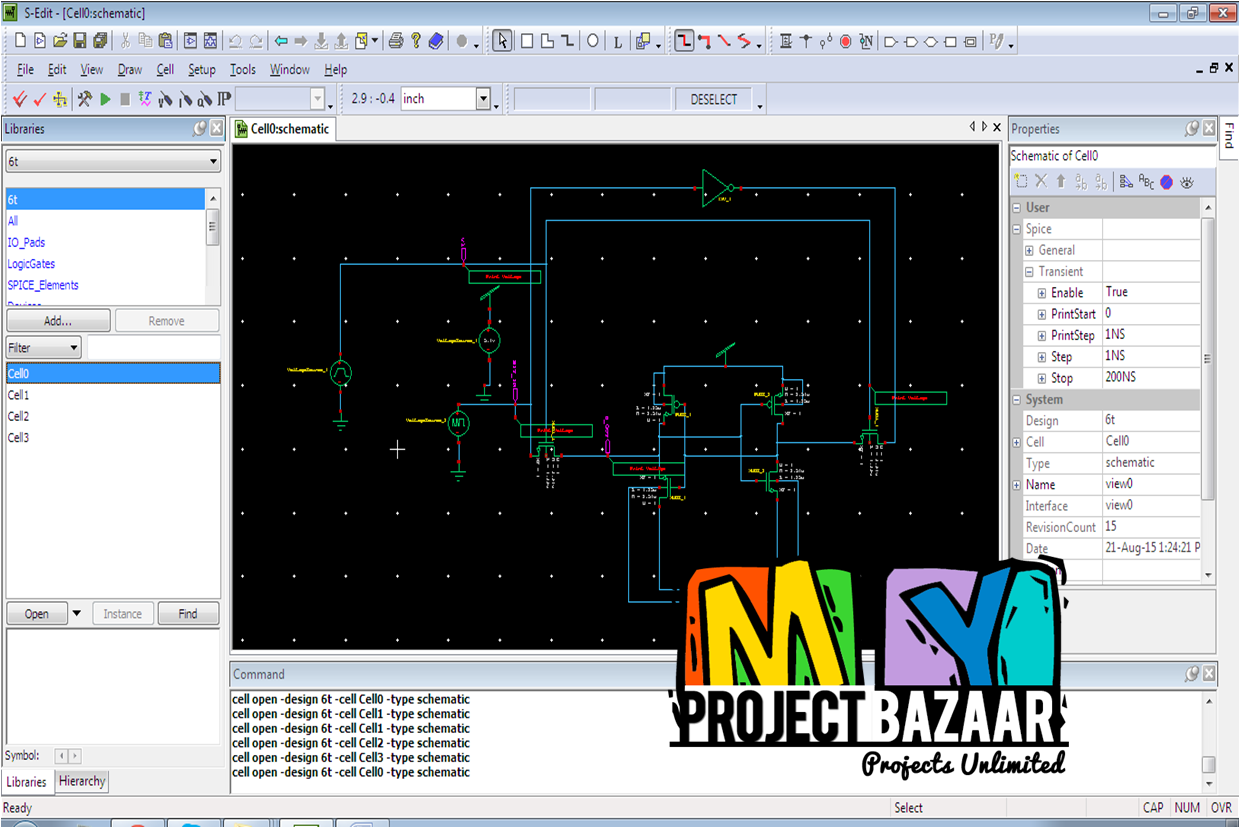

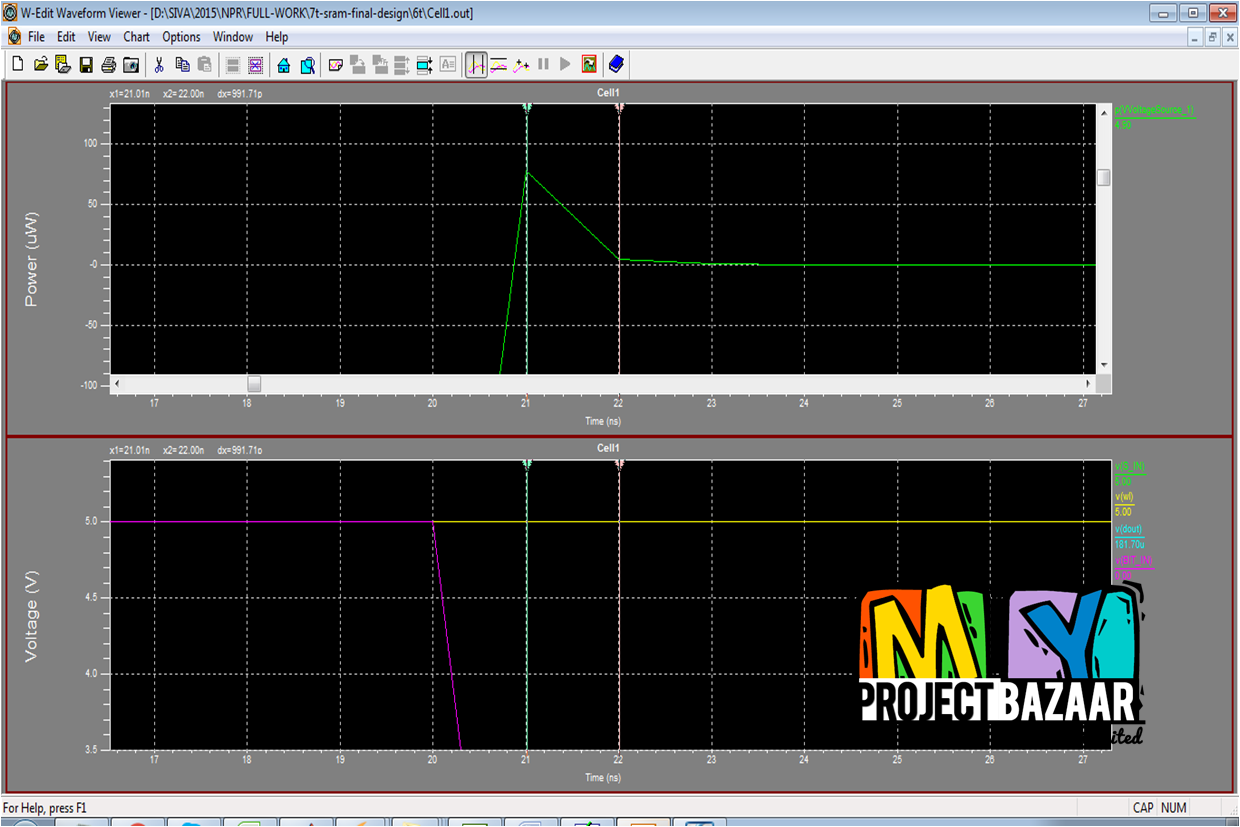

Abstract— An 8T Low-Voltage and Low-Leakage Half-Selection Disturb-Free SRAM Using Bulk-CMOS and FinFETs. < Final Year Projects 2016 > we present a new 8T design for static random access memory (SRAM) cell that is based on traditional Si technology and reduces leakage power considerably compared with a conventional design. Proposed design can be fully functional at smaller supply voltages over the conventional 6T SRAM cell. To verify the proposed design, a 32 kb SRAM is designed and simulated in 90 nm CMOS technology using the proposed 8T and conventional 6T SRAM cells. Operating at their VDD min, simulations show improvement of 58% and 67% for write and read power per operation, respectively, for our design. To address the challenge of half-selection during write operation, a new low-power internal write-back scheme is presented. Finally, designing proposed cell using fin-shaped field effect transistors shows less sensitivity to variations and also improvement of 2.08 × in read static noise margin at VDD=1 .0 V over bulk-CMOS-based SRAM cell.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains | |

|---|---|

| Programming Language |