A Low-Power Edge Detection Image Sensor Based on Parallel Digital Pulse Computation

Product Description

A Low-Power Edge Detection Image Sensor Based

on Parallel Digital Pulse Computation

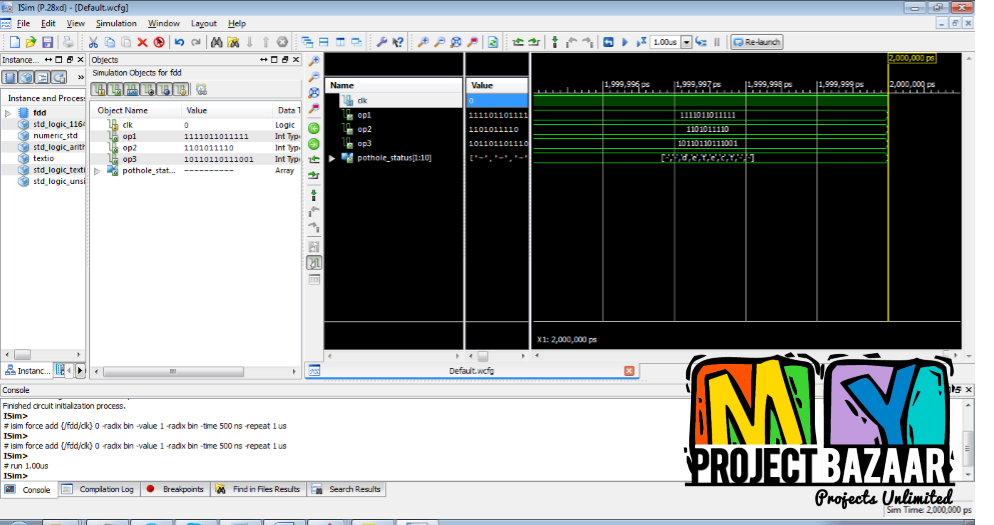

Abstract— A Low-Power Edge Detection Image Sensor Based on Parallel Digital Pulse Computation. An all-digital low-power < Final Year Projects 2016 > CMOS edge detection image sensor array is presented. Each pixel contains a voltage-controlled ring oscillator to achieve low-power and cost-efficient digital-only edge detection. While conventional edge detection methods require high computing power and large chip area to process intensity maps, this work implements an all-digital parallel processing algorithm that detects differences between neighboring pixel pairs on chip, hence reducing the aforementioned power and cost overheads. In particular, a simple column-shared frequency comparator enables low-power operation by eliminating arithmetic computations with large memory requirement. Such a simple edge detection algorithm allows the processor area to be less than 16% of the entire image sensor, therefore maximizing the proportion of active optical area. The prototype image sensor presented in this work is fabricated using a four-metal 180-nm CMOS image sensor process and contains 105 × 92 pixels. An individual pixel size is 8 × 8 µm with a fill factor of 11.69%, while the total chip area is 1 × 1.3 mm 2. The image sensor exhibits a frame rate of 30 frames/s and a power consumption of 8 mW, which is 27.7 nW/pixel/frame at VDD of 1.6 V.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|