Low Power Address Generator for Memory Built-In Self Test

Product Description

Low Power Address Generator for Memory Built-In Self Test

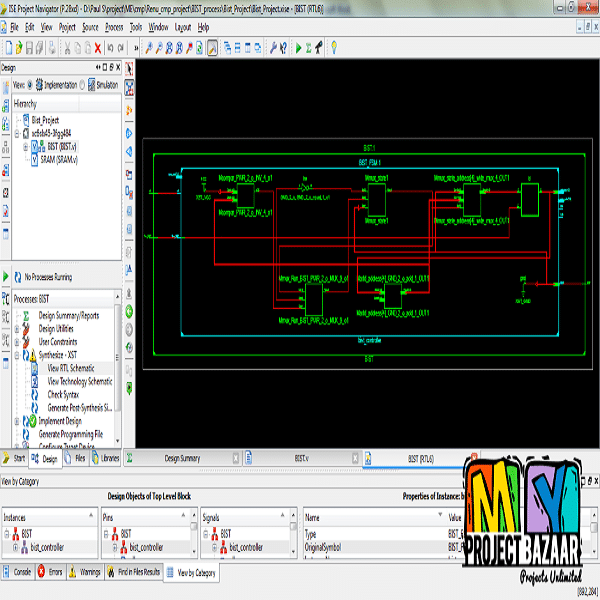

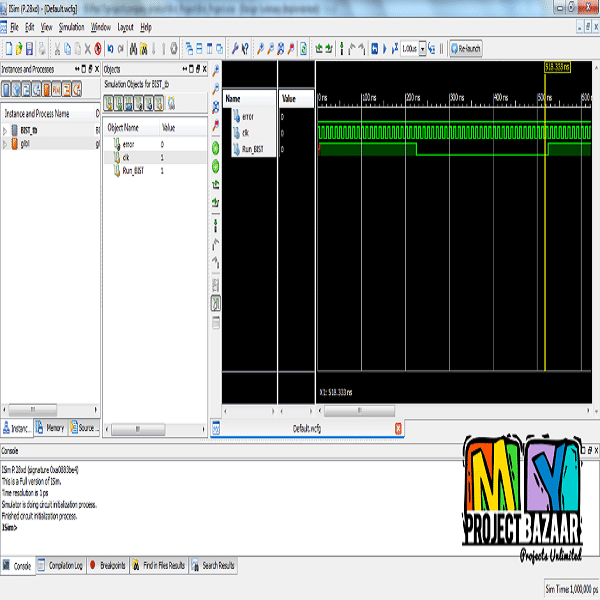

Abstract-Memory is one of the basic computer components that is intensively accessed. Therefore, it is more likely to be affected by manufacturing faults rather than other components in the System on Chip (SoC). Memory Built-in Self Test (MBIST) is the most commonly used to test embedded memories. Although many algorithms were developed for MBIST, only few of these techniques focus on reducing the test power which plays an important role in evaluating the effectiveness of the test. This paper deals with reducing the switching activity in the address bus when testing SRAM of personal devices. The MBIST architecture was programmed using VHDL and then five address generators were simulated using Xilinx ISE tools and compared with each others in terms of their switching activity which is proportional to the test power.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+