A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks

Product Description

A Low-Latency and Low-Power Hybrid Scheme for On-Chip Networks

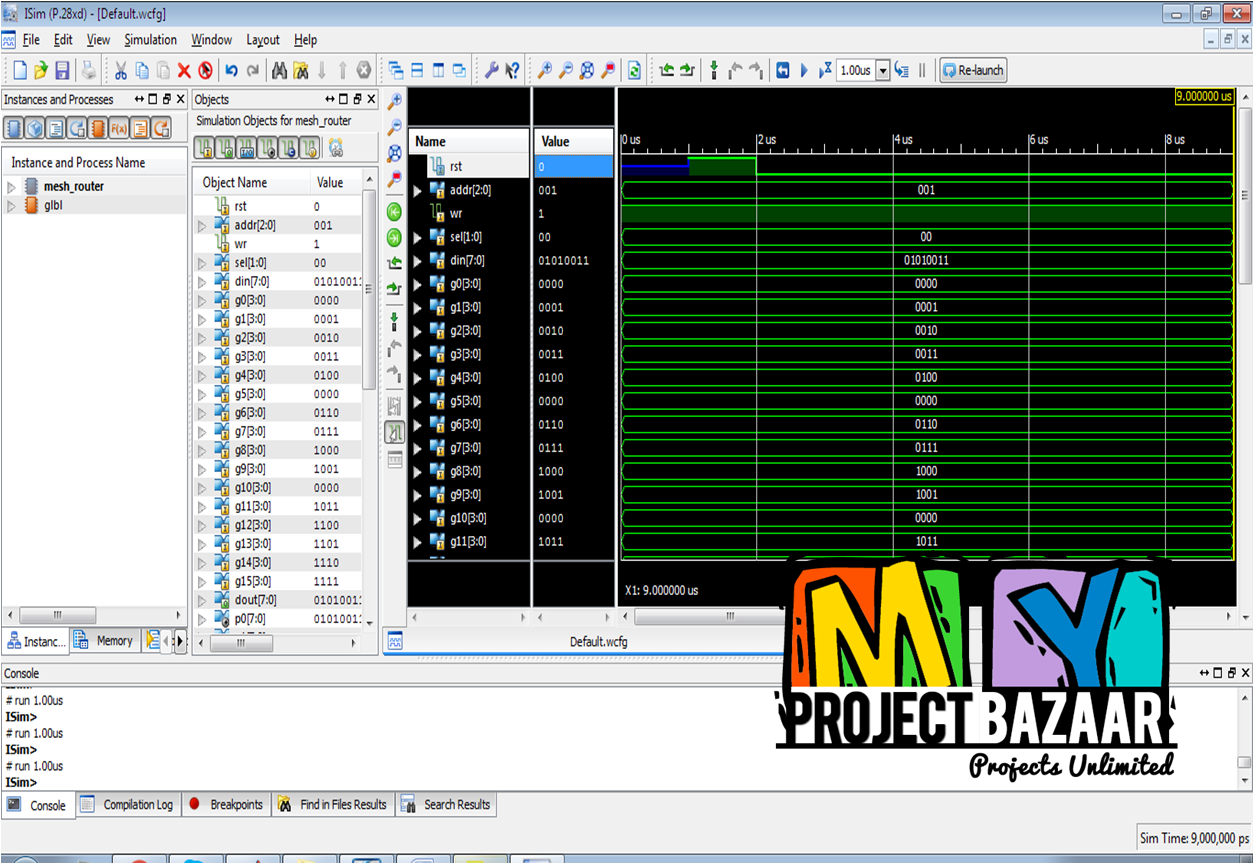

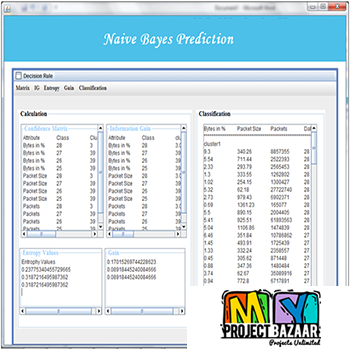

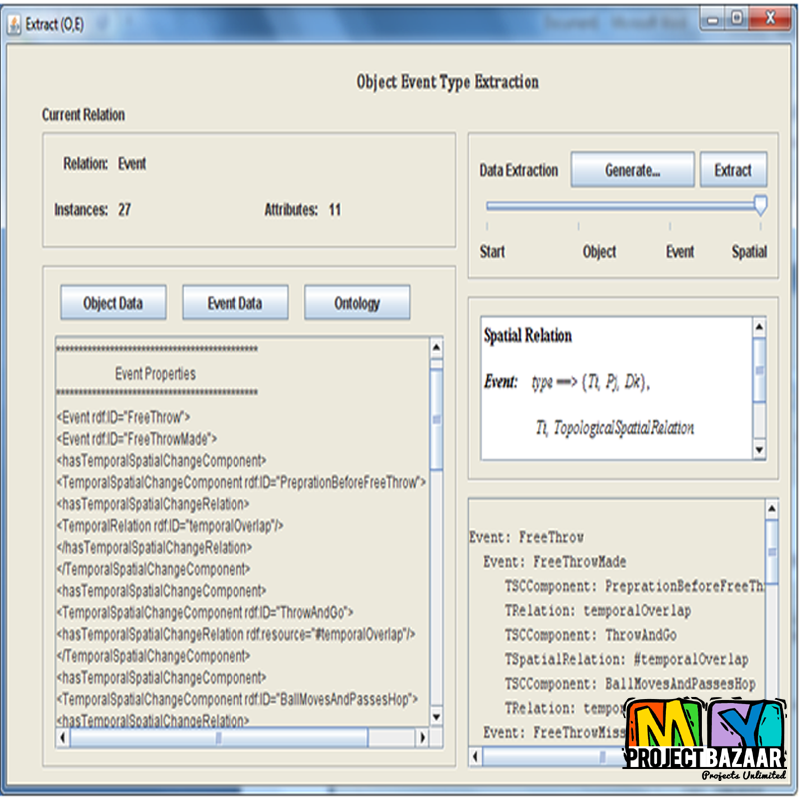

Abstract—Network-on-chip (No C) has emerged as a vital factor that determines the performance and power consumption of many-core systems. This paper proposes a hybrid scheme for No Cs, which aims at obtaining low latency and low power consumption. In the presented hybrid scheme, a novel switching mechanism, called virtual circuit switching, is proposed to intermingle with circuit switching and packet switching. Flits traveling in virtual circuit switching can traverse the router with only one stage. In addition, multiple virtual circuit-switched < Final Year Projects 2016 > VCS connections are allowed to share a common physical channel. Moreover, a path allocation algorithm is proposed in this paper to determine VCS connections and circuit-switched connections on a mesh-connected No C, such that both communication latency and power are optimized. A set of synthetic and real traffic workloads are exploited to evaluate the effectiveness of the proposed hybrid scheme.

Including Packages

Our Specialization

Support Service

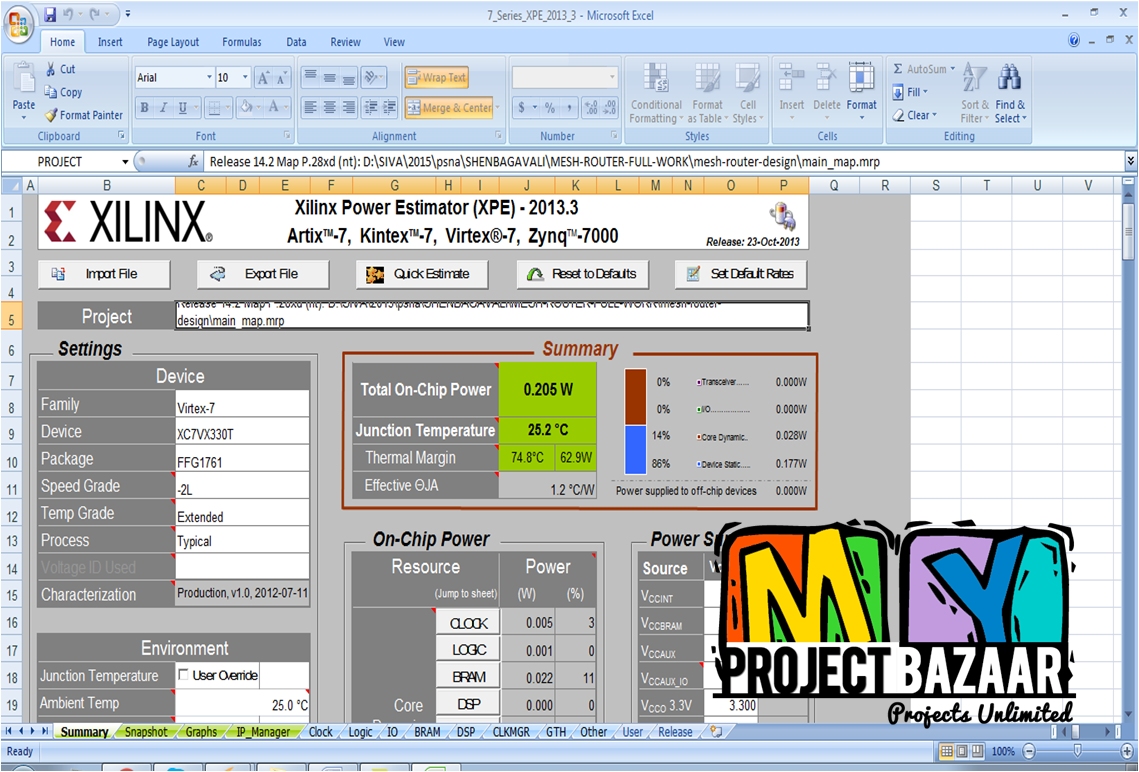

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|