Low‑power half‑select free single‑ended 10 transistor SRAM cell

Product Description

LLow‑power half‑select free single‑ended 10 transistor SRAM cell

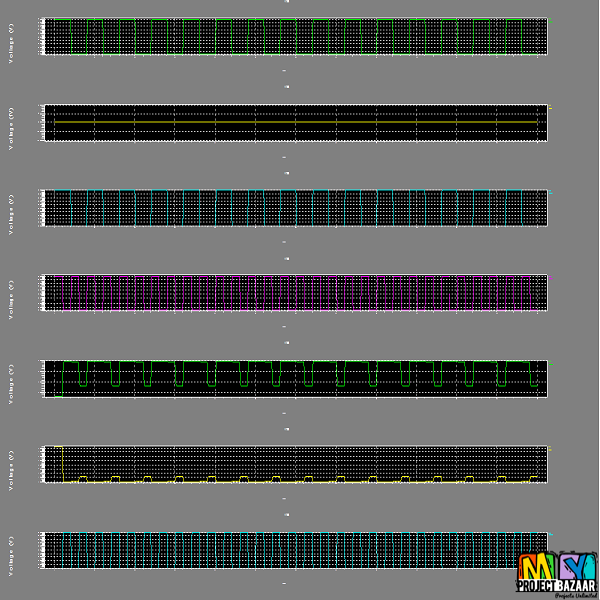

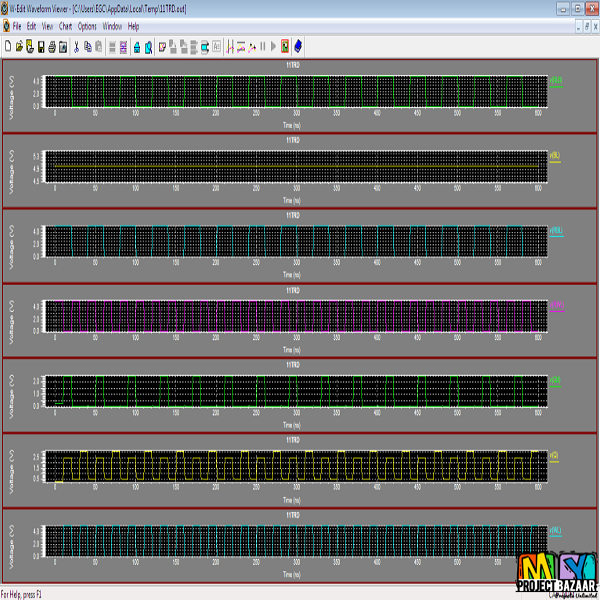

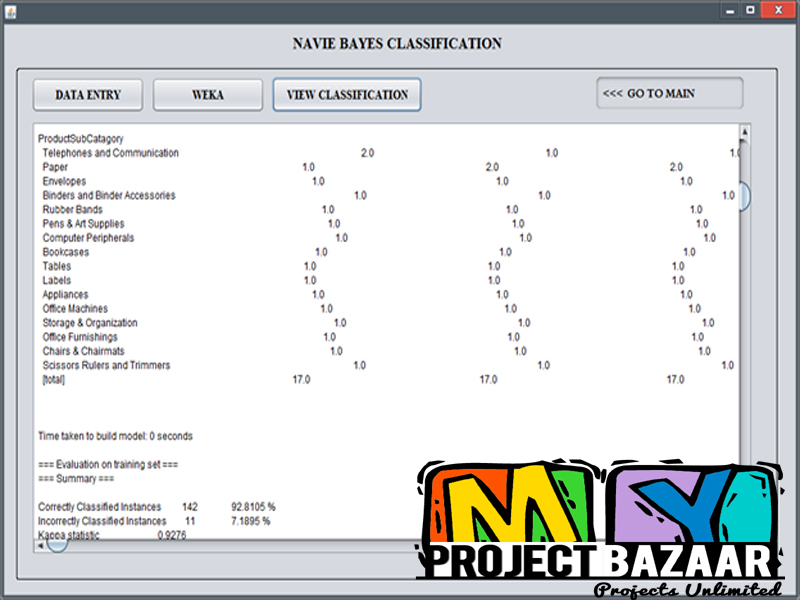

Abstract—Abstract This paper proposes a novel sub threshold 10T SRAM cell. The proposed design removes the half-select issue which is a problem in SRAM array as observed in the case of conventional 6T and 8T cells. Since the proposed cell is free from half-select disturb, bit-interleaving scheme can be implemented. A bit-interleaved architecture helps to reduce errors in multiple bits of a single word. This makes the proposed design immune to soft error caused by α particles or high-energy cosmic rays. The proposed cell uses data-dependent stack PMOS switching scheme (DSPS) to reduce the write access time and improve the write-ability.A single-ended read decoupled scheme used to perform read operation enhances the read stability. Various design metrics of the proposed SRAM cell have been compared with previously proposed cells such as SBI9T, DF9T and UDVS10T. The proposed cell shows 1.07×, 2.89× and 13.78× improvement in write access time while writing ‘0’ as compared to the SBI9T, DF9T and UDVS10T,respectively at a VDD of 0.4 V. The proposed cell shows lesser spread in write delay as compared to DF9T cell,which signifies lower variability. There is 8.4, 10.3 and 6.5 % improvement in WSNM when compared to the three cells mentioned above, respectively. Also, 27.3 and 2.02 % improvements can be observed in RSNM when compared to the SBI9T and DF9T at a supply voltage of 0.4 V. RSNM of UDVS10T is same as that of the proposed design.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+