Implementation of Fixed and Floating Point Square Root Using Nonrestoring Algorithm on FPGA

Product Description

Implementation of Fixed and Floating Point Square Root Using Nonrestoring Algorithm on FPGA

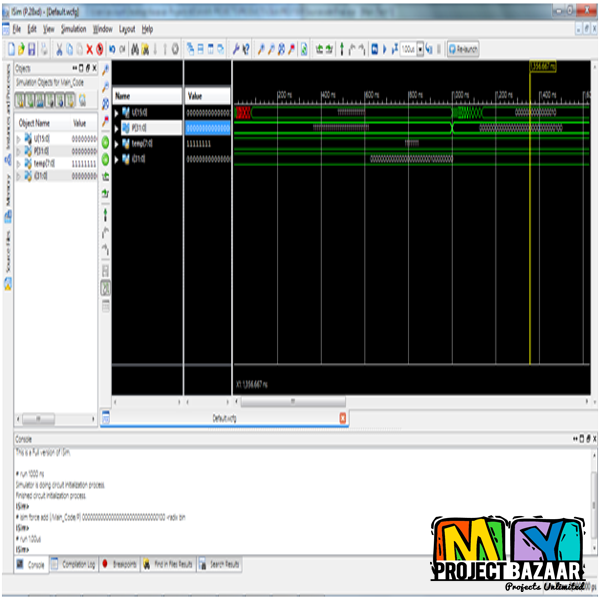

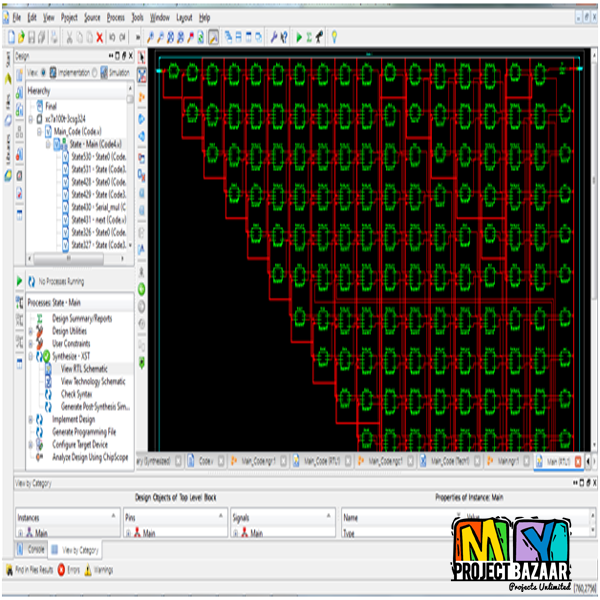

Abstract—Square root is one of the fundamental arithmetic operations in signal and image processing algorithms. This article presents a novel pipelined architecture to implement N-bits fixed point square root in FPGA using non-restoring algorithm. Pipelining hazards were avoided by modifying the non-restoring algorithm resulting in a 30% improved latency time. Furthermore, the proposed architecture is flexible and can be modified as per the need of an application. < Final Year Project > The performance of the proposed system, as a function of execution time and power consumption per operation, has been compared with other floating point pipelined implementations. It is demonstrated that the proposed system is ∼ 2 times efficient compared to its counterparts.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet