Glitch Energy Reduction and SFDR Enhancement Techniques for Low-Power Binary-Weighted Current-Steering DAC

Product Description

Glitch Energy Reduction and SFDR Enhancement Techniques for Low-Power Binary-Weighted Current-Steering DAC

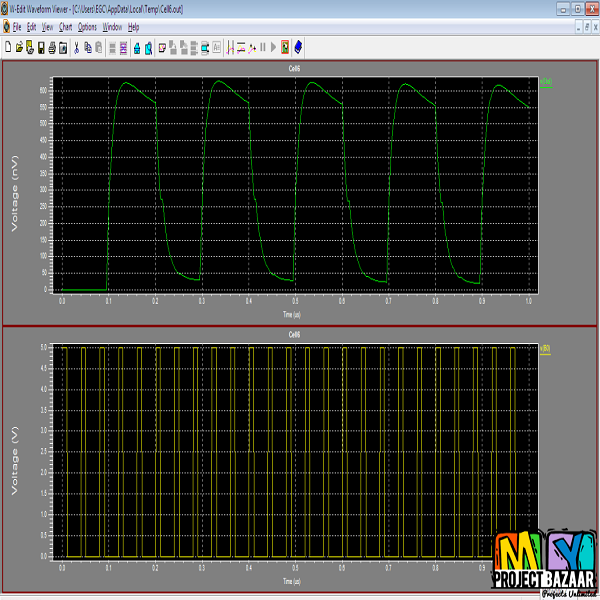

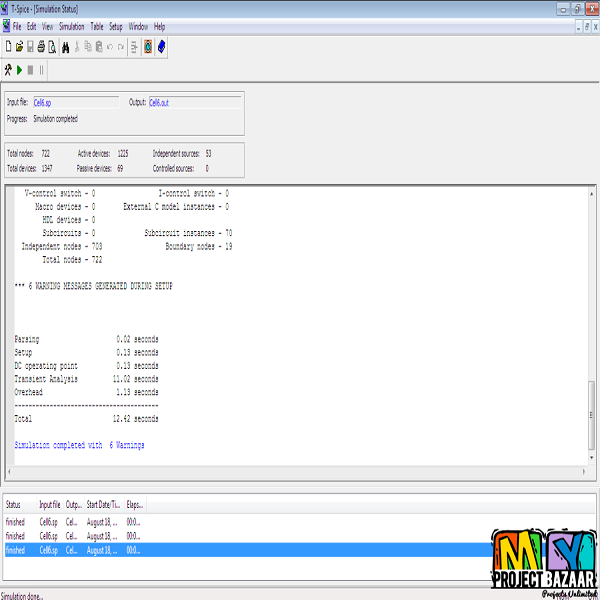

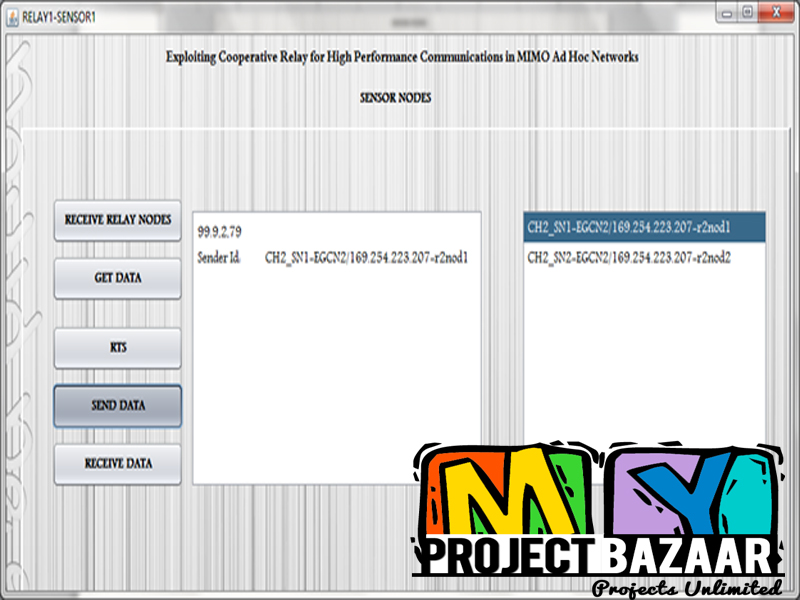

Abstract— A glitch reduction approach by dynamic capacitance compensation of binary-weighted current switches in a current-steering digital-to-analog converter (DAC). The method was proved successfully by a 10-bit 400-MHz pure binary-weighted current-steering DAC with a minimum number of retiming latches. The experiment results yield very low-glitch energy during major carry transitions at output, which is < 1 pVs. This brief utilizes a layout structure to improve the spurious-free dynamic range at high signal frequencies. This chip was implemented in a standard 0.18-µ m CMOS technology and consumes 20.7 mW at 400 MS/s. Current-steering digital-to-analog converters (DACs) perform an important role in communication and video systems. Current-steering DACs have the advantages of speed, linearity, and power efficiency. There are three different architectures to implement the switched current source array, binary, unary, and segmented. Accounting for power consumption, chip size, and circuit complexity, the binary-weighted architecture is still a good candidate for medium-to-high resolution and sampling rate. It achieves both static and dynamic specifications at low cost. The design approach proposed in this brief can be applied to the LSB part for segmented DACs as well. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+