FPGA Based Implementation & Power Analysis of Parameterized Walsh Sequences

Product Description

FPGA Based Implementation & Power Analysis of Parameterized Walsh Sequences

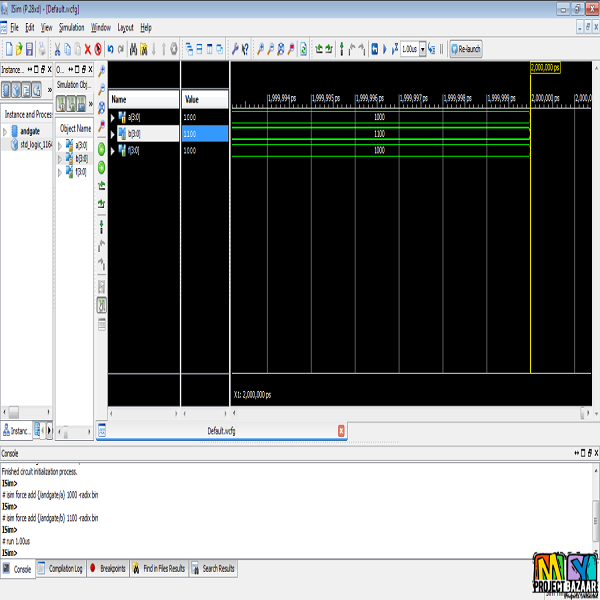

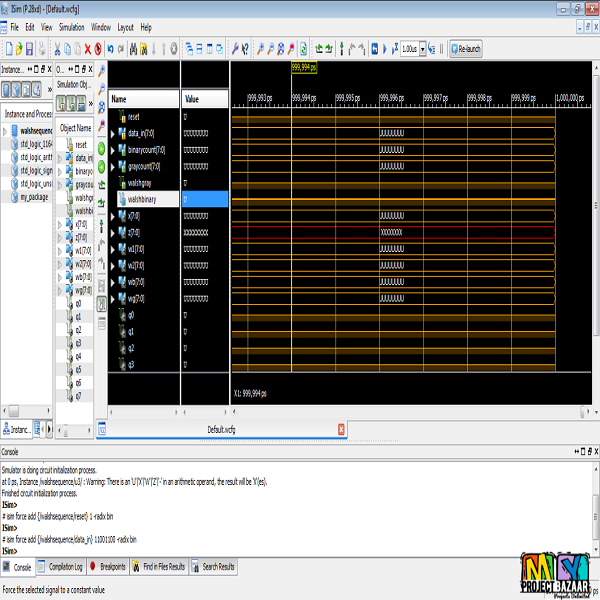

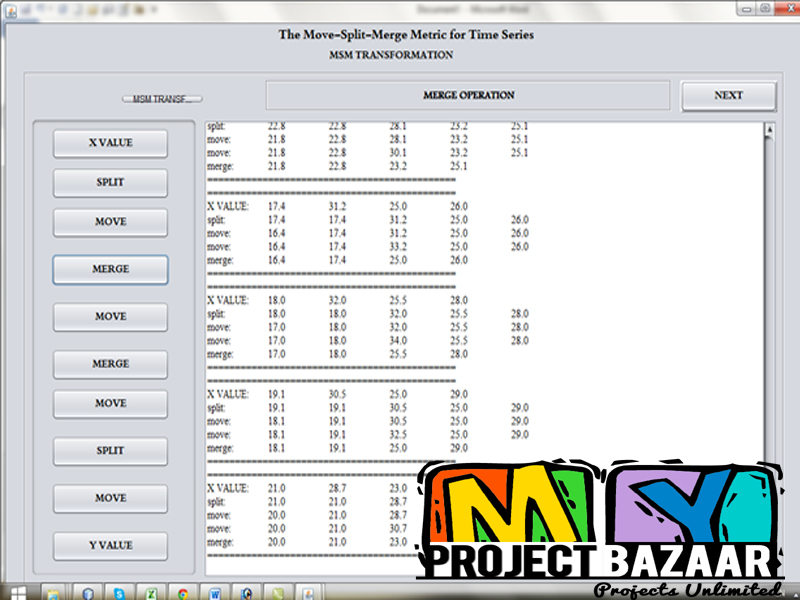

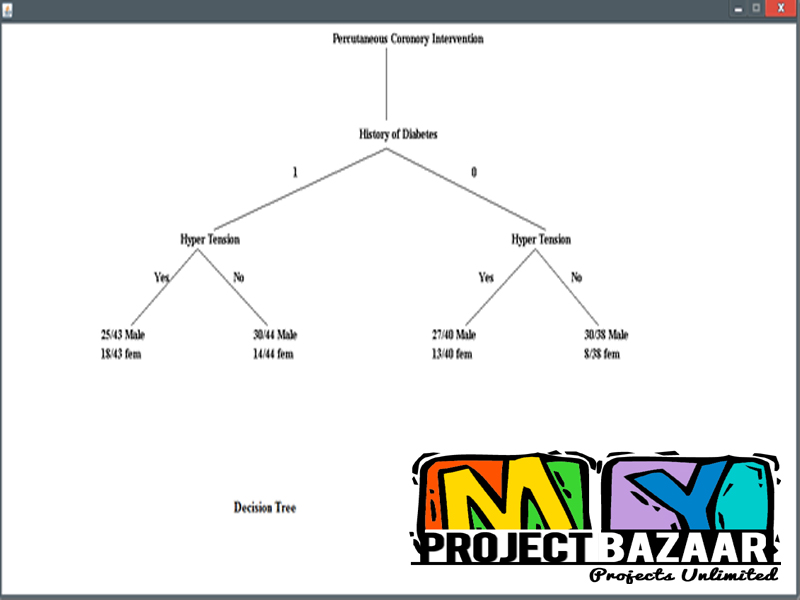

Abstract—Abstract This paper presents FPGA based implementation of the theory which replaces a general Sine and cosine function by set of orthogonal functions i.e. Walsh function. The paper further compares Parameterized ‘Serial In Serial Out’ architectures based on classical counter approach. The investigation consider FPGA parameters like Area, Speed and Power and shows that using Gray-increment based architecture instead of Binary saves 6mW of power per symbol (64 Walsh chips per symbol) with 30% reduction in area. The design is implemented in VHDL code, simulated in MATLAB System Generator environment and validated with MATLAB Simulink Model. The design targeted Xilinx Virtex-5 “XC5VLX50T-1ff1136” FPGA device for the implementation and comparison. The design found their uses in many popular applications like Software Define Radio (SDR) including multiuser communications such as CDMA, WCDMA,VLSI testing, pattern recognition as well as image and signal processing.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+