Fast Design Space Exploration using Vivado HLS: Non-Binary LDPC Decoders

Product Description

Fast Design Space Exploration using Vivado HLS: Non-Binary LDPC Decoders

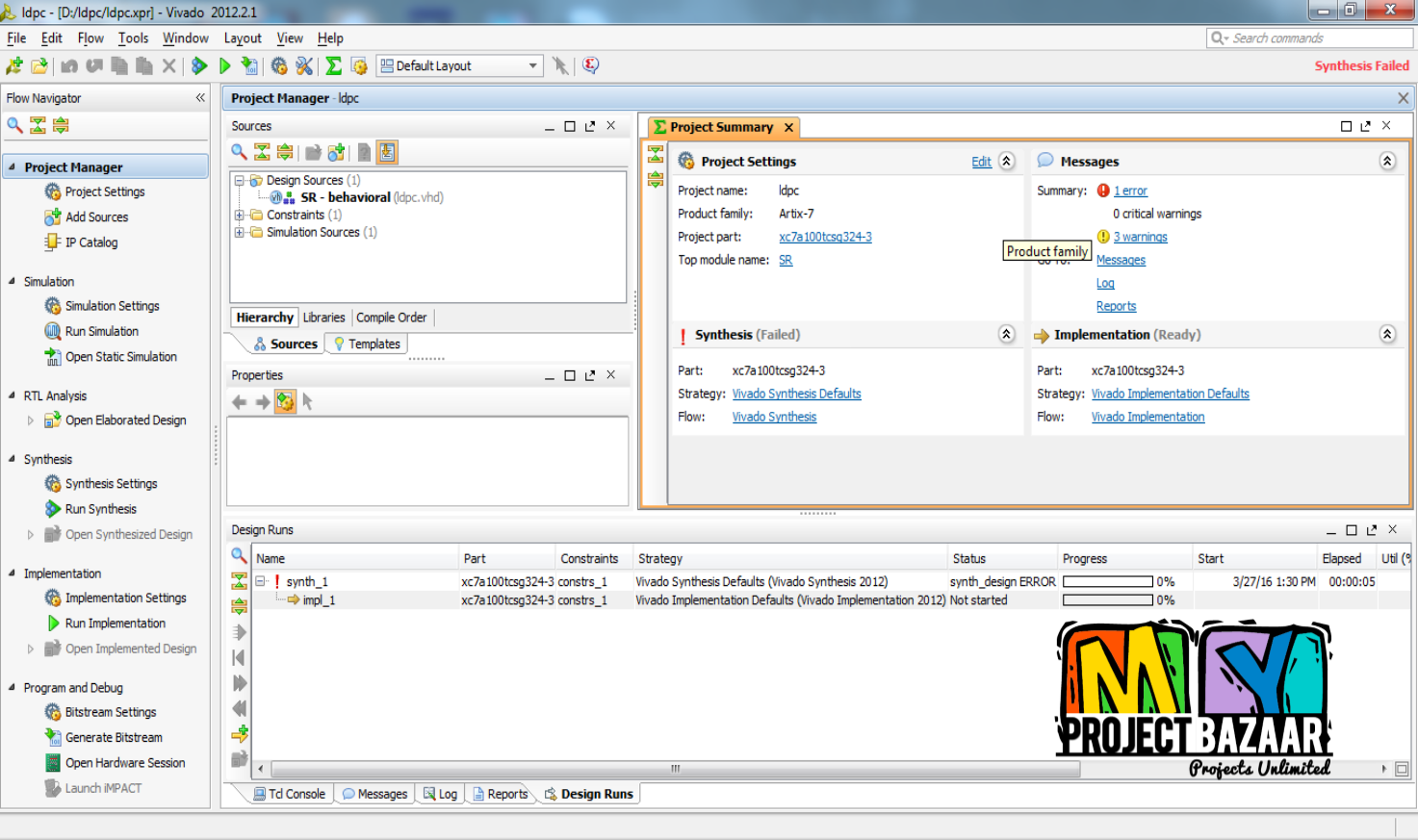

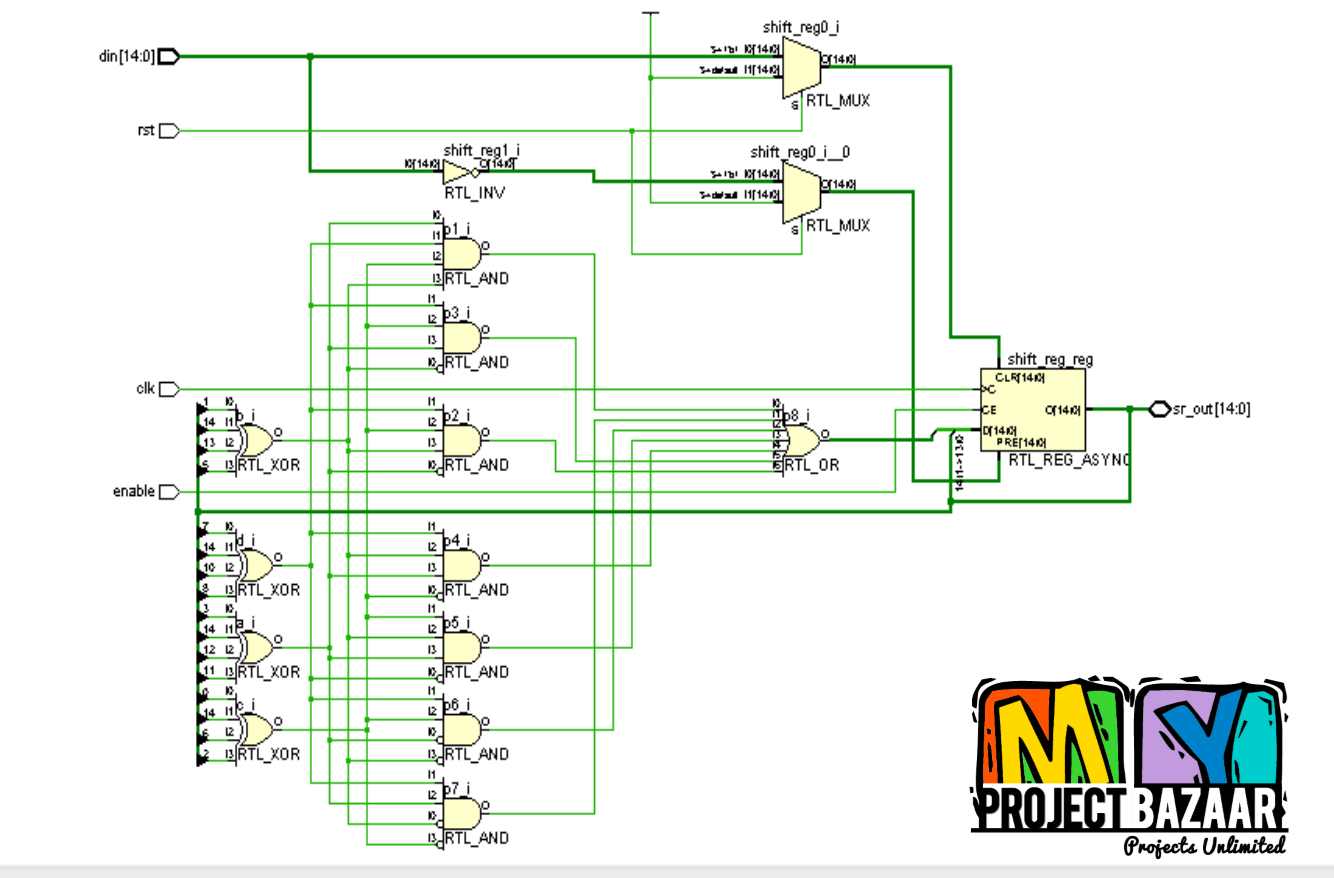

Abstract— Fast Design Space Exploration using Vivado HLS: Non-Binary LDPC Decoders. Computing on field-programmable gate arrays < Final Year Projects 2016 > FPGAs has been receiving continued interest as it provides high performance at relatively low power budgets, while avoiding the high non-recurring engineering (NRE) costs associated with ASIC designs. However, FPGA development is typically performed using register transfer level (RTL) languages which make the design process protracted and error-prone when compared to software design flows. To ease these problems, high-level synthesis (HLS) tools have been introduced which abstract away the RTL architecture description from the designer. In this work we explore the design space of a non-binary GF (q) low-density parity-check (LDPC) decoder using Vivado HLS and compare it with state-of-the-art RTL designs.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|