Bit-Interleaving-Enabled 8T SRAM With Shared Data-Aware Write and Reference-Based Sense Amplifier

Product Description

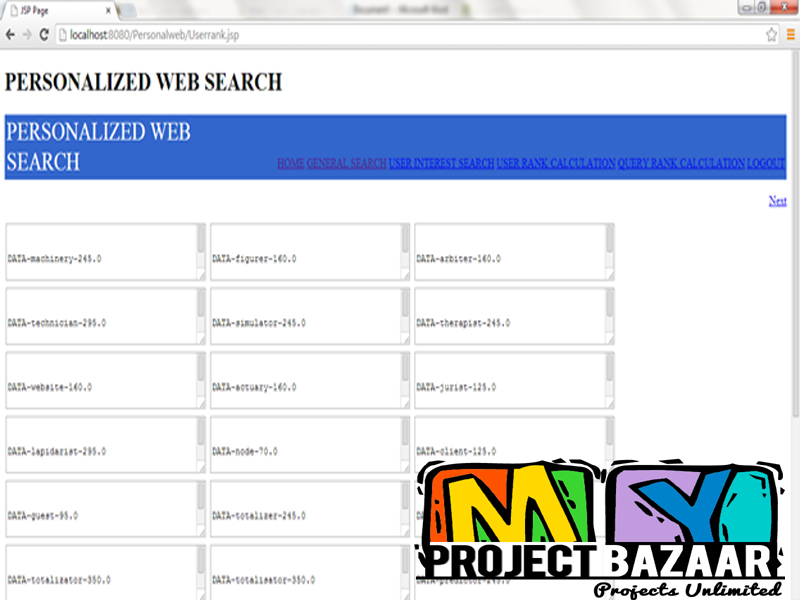

Bit-Interleaving-Enabled 8T SRAM With Shared Data-Aware Write and Reference-Based Sense Amplifier

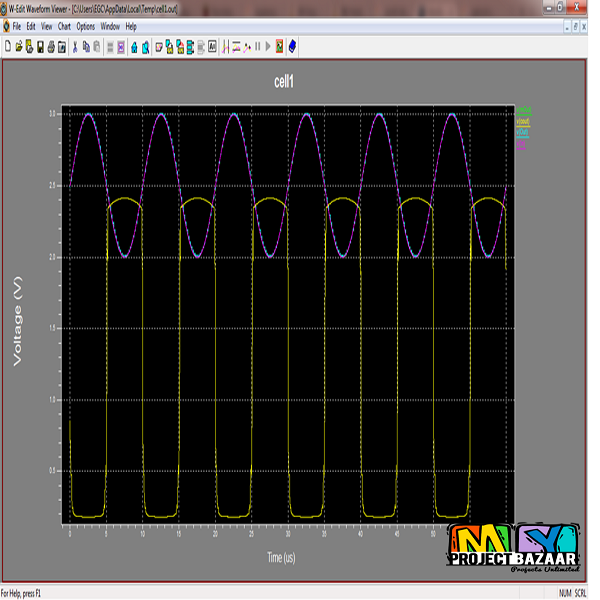

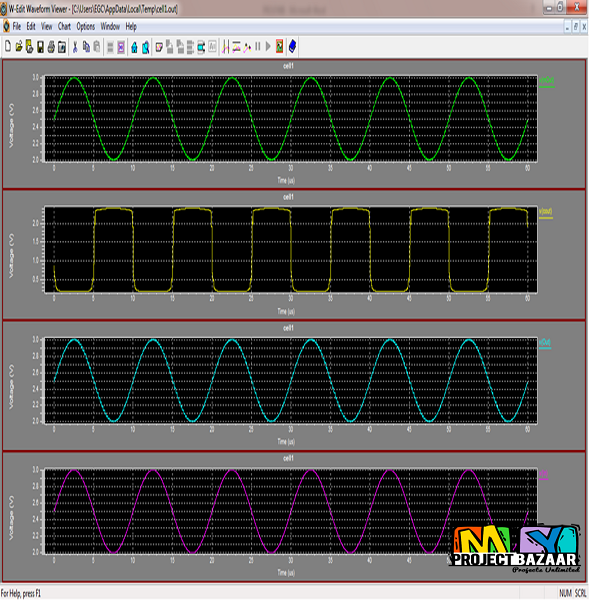

Abstract— The design of a low-voltage static random access memory (SRAM) for biomedical chip applications. The SRAM is designed using a standard 8T bit cell, featuring a shared data-aware write scheme and a differential reference-based sense amplifier. The proposed techniques make it possible for the 8T SRAM to use bit-interleaving architecture and address the half-select problem, achieving area efficiency and power reduction. A 96-kb 8T SRAM test chip is implemented in a 65-nm CMOS process to verify the proposed schemes, which operates functionality at a VDD minof 0.36 V and has a power consumption of 5.1 μW. In these devices, battery-powered or batteryless supplies are used, and the operational frequency of the signals ranges from a few hundreds of kilohertz to tens of megahertz. Thus, there is an extreme need to minimize the power dissipation for long-term operation to extend battery lifetime. One of the most straight and effective methods is to scale the supply voltage aggressively to the subthreshold regions since the active power has a quadratic dependence on voltage and the leakage power is exponentially related to the voltage. However, reducing voltage would degrade the robust-ness of the circuits and even cause the systems to be prone to malfunction. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+