An Efficient Hybrid-Switched Network-on-Chip for Chip Multiprocessors

Product Description

An Efficient Hybrid-Switched Network-on-Chip for Chip Multiprocessors

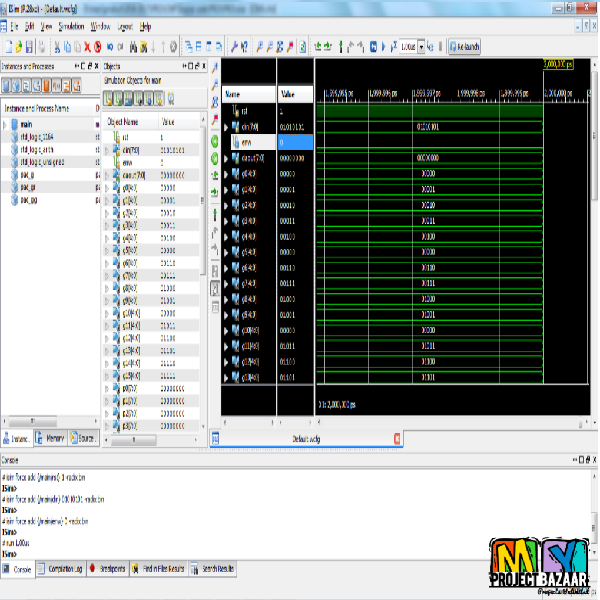

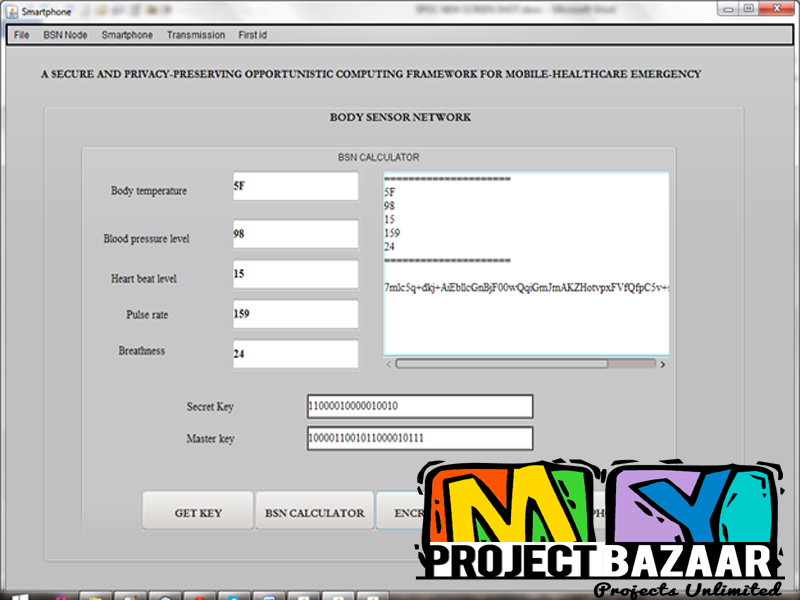

Abstract— Chip multiprocessors (CMPs) re quire a low-latency interconnect fabric network-on-chip (NoC) to minimize processor stall time on instruction and data accesses that are serviced by the last-level cache (LLC). While pack et-switched mesh interconnects sacrifice performance of many-core processors due to NoC- induced delays, existing circuit-switched interconnects do not offer lower network delays as they cannot hide the time it takes to set up a circuit. To address this problem, this work introduces CIMA—a hybrid circuit-switched and pack et-switched mesh -based interconnection network that affords low LLC access delays at a small area cost. CIMA uses virtual cut-through (VCT) switching for short request packets , and benefit s from circuit switching for longer, delay sensitive response packets . While a request is being served by the LLC, CIMA attempts to set up a circuit for the corresponding response packet. By the time the request packet is served and the response gets ready, a circuit has already been prepared, and as a result, the response packet experiences short delay in the network. A detailed evaluation targeting a 64- core CMP running scale-out work loads reveals that CIMA improves system performance by 21 percent over the state-of-t he-art hybrid circuit-packet-switched network.< final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+