Efficient FPGA and ASIC Realizations of a DA-Based Reconfigurable FIR Digital Filter

Product Description

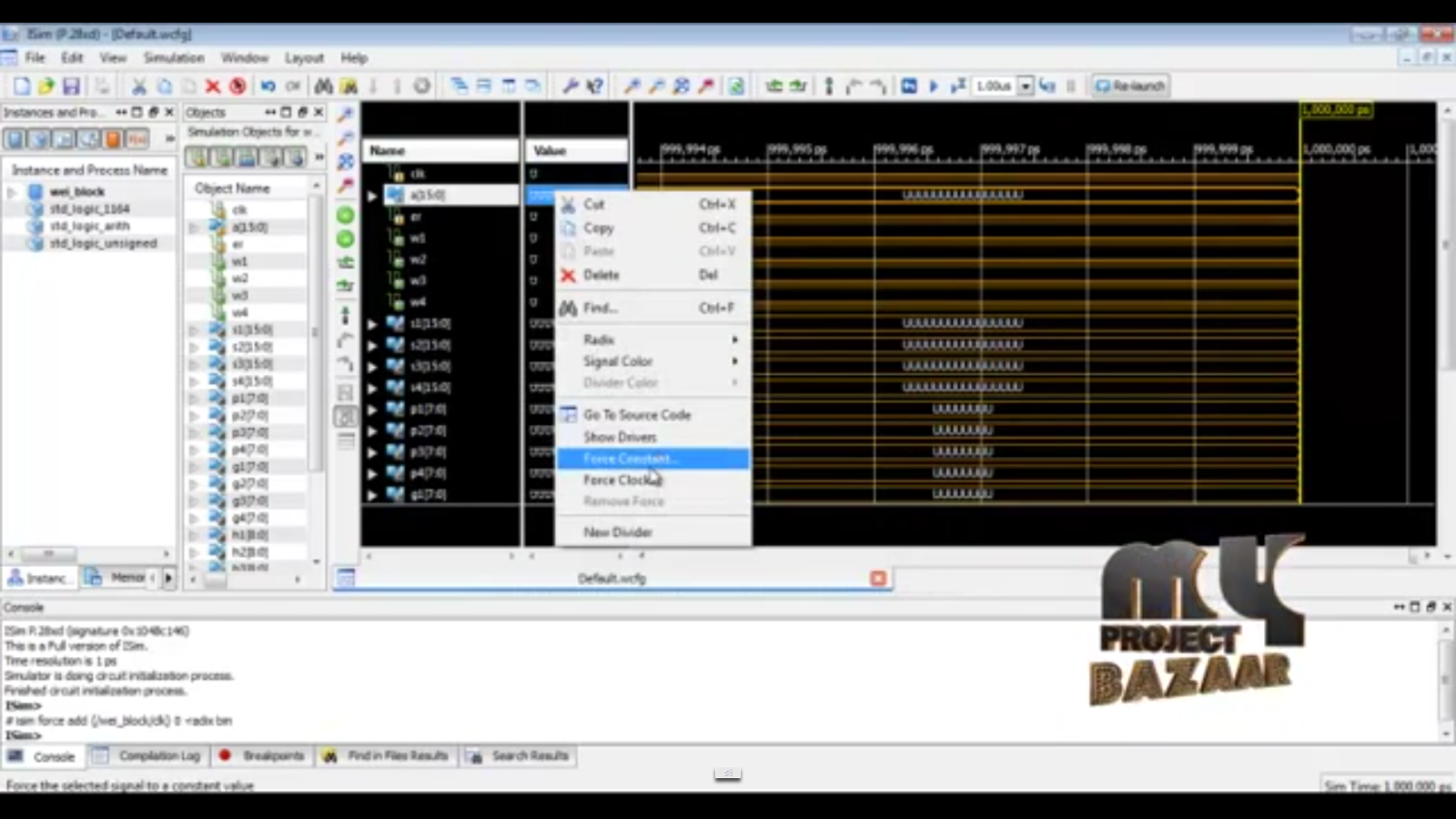

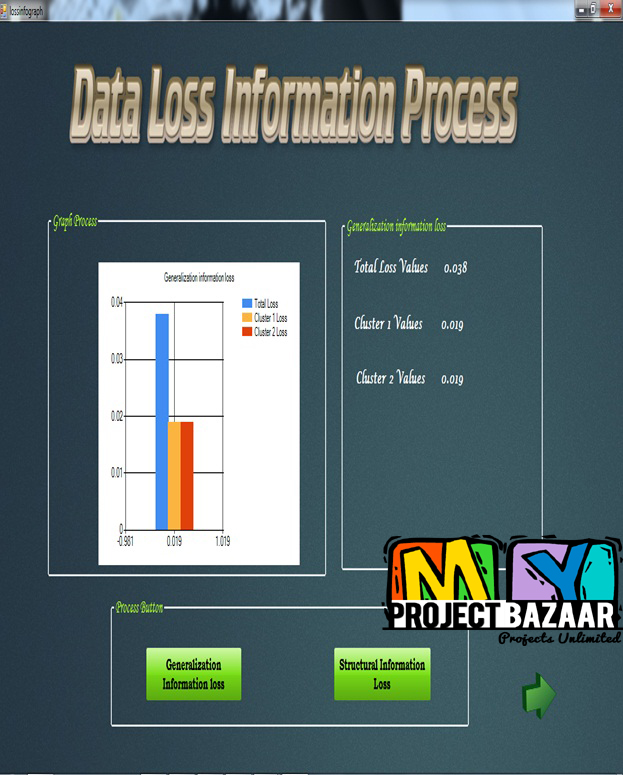

Abstract—This brief presents efficient distributed arithmetic (DA)-based approaches for high-throughput reconfigurable implementation of finite-impulse response (FIR) filters whose filter coefficients change during runtime. Conventionally, for reconfigurable DA-based implementation of FIR filter, < Final Year Projects > the lookup tables (LUTs) are required to be implemented in RAM and the RAM-based LUT is found to be costly for ASIC implementation. Therefore, a shared-LUT design is proposed to realize the DA computation. Instead of using separate registers to store the possible results of partial inner products for DA processing of different bit positions, registers are shared by the DA units for bit slices of different weightage. The proposed design has nearly 68% and 58% less area-delay product and 78% and 59% less energy per sample than the DA-based systolic structure and the carry save adder (CSA)-based structure, respectively, for the ASIC implementation. A distributed-RAM-based design is also proposed for the field-programmable gate array (FPGA) implementation of the reconfigurable FIR filter, which supports up to 91 MHz input sampling frequency and offers 54% and 29% less the number of slices than the systolic structure and the CSA-based structure, respectively, when implemented in the Xilinx Virtex-5 FPGA device (XC5VSX95T-1FF1136).

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+