CMCS: Current-Mode Clock Synthesis

Product Description

CMCS: Current-Mode Clock Synthesis

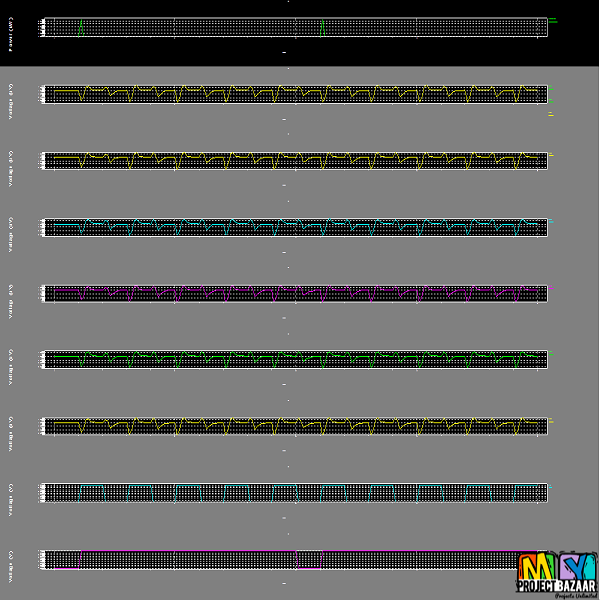

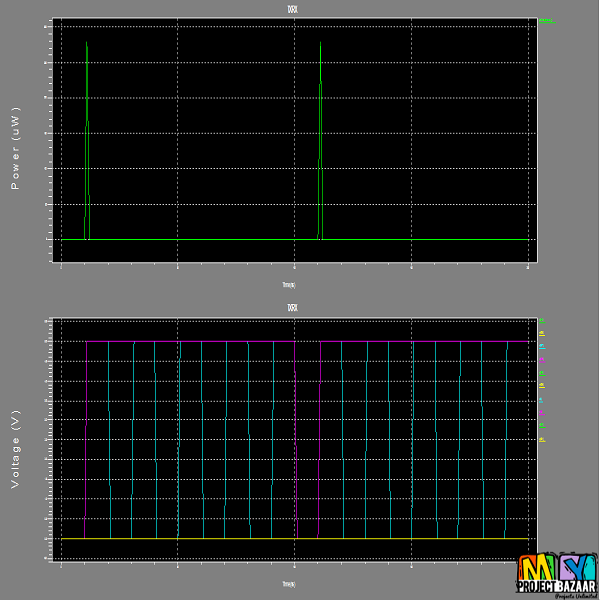

Abstract— In a high-performance VLSI design, the clock network consumes a significant amount of power. While most existing methodologies use voltage-mode (VM) signaling, these clock distributions lose a tremendous amount of dynamic power to charge/discharge the large global clock capacitance. New circuit approaches for current-mode (CM) clocking save significant clock power, but have been limited to only symmetric networks, while most application specific integrated circuits have asymmetric clock distributions. In this paper, we propose the

first CM clock synthesis (CMCS) methodology to reduce the overall clock network power with low skew. The method can

integrate with traditional clock routing followed by transmitter and receiver sizing. We validate the proposed methodology using ISPD 2009 and 2010 industrial benchmarks using an extracted SPICE model distributed in 1.4–275.6-mm2 area and consists of 81–2249 sinks. This methodology saves 39%–84% average power with similar skew on the benchmarks using 45-nm CMOS technology simulation of clock frequencies range from 1–3 GHz. In addition, the CMCS methodology takes 2.4−9.1× less running time and consumes 20%–26% less transistor area compared with synthesized, buffered VM clock distributions. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+