Built-In Self-Test Methodology With Statistical Analysis for Electrical Diagnosis of Wearout in a Static Random Access Memory Array

Product Description

Built-In Self-Test Methodology With Statistical Analysis for Electrical Diagnosis of Wearout in a Static Random Access Memory Array

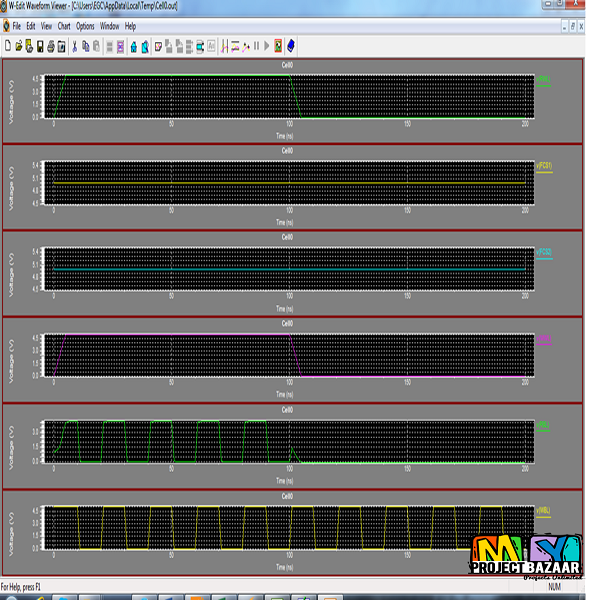

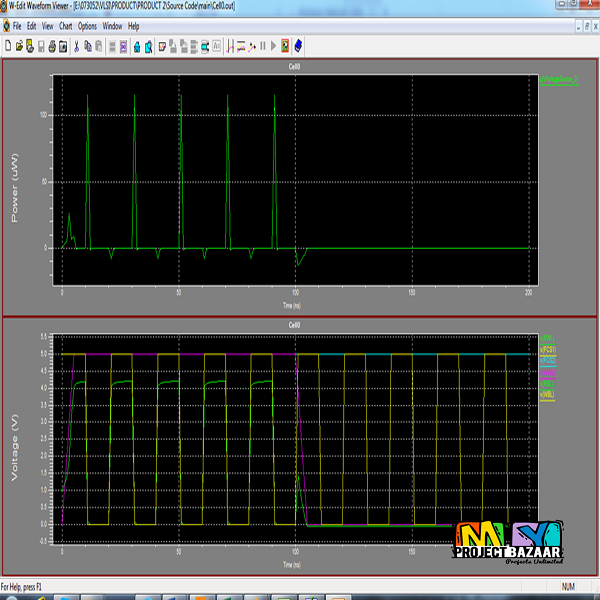

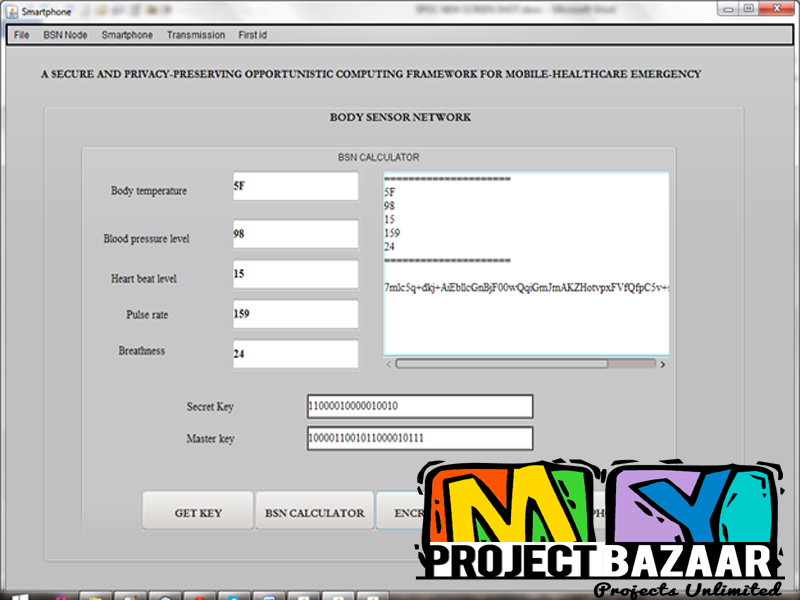

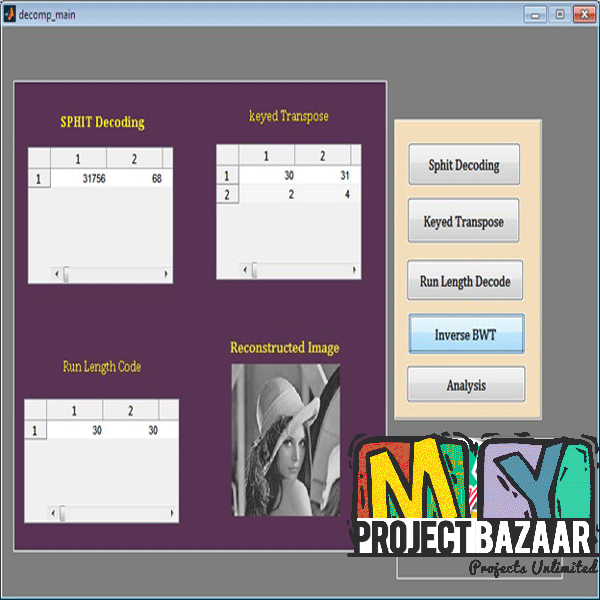

Abstract— An electrical diagnosis methodology for a variety of wearout mechanisms, including back-end time-dependent dielectric breakdown (TDDB), electromigration, stress-induced voiding, gate oxide TDDB, and bias temperature instability, in an SRAM array. Firs t, the built-in self-test (BIST) system detects wearout and identifies the locations of the faulty cells. Next, the physical location of the failure sites within SRAM cells is determined. There are some fault sites for different mechanisms which result in exactly the same electrical failure

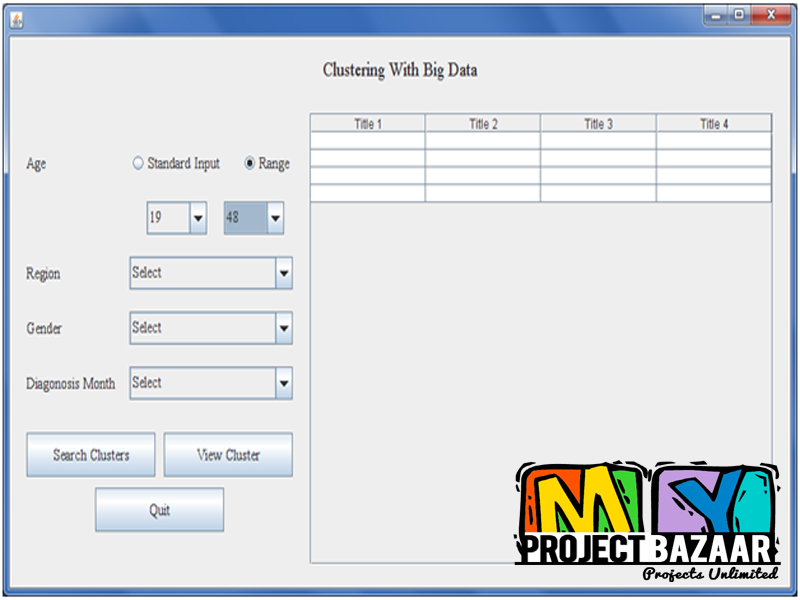

signature. For these faulty sites, the cause of failure probabilities for each wearout mechanism is estimated by matching the observed failure rate from BIST and the failure rate distribution computed by simulation and as a function of circuit use scenarios. The estimation of wearout distributions is helpful in determining the wearout limiting mechanisms in the field. Despite the use of more vulnerable devices, SRAM systems,in electronic applications, from mobile devices, personal computers, and automatic vehicles to flight controllers, need to be fault tolerant and reliable in order to guarantee safe operation. According to the International Technology Roadmap for

Semiconductors, high-performance processors are expected to consist of 82% memory on average. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+