Analysis of Leakage Current and Leakage Power Reduction during Write operation in CMOS SRAM Cell

Product Description

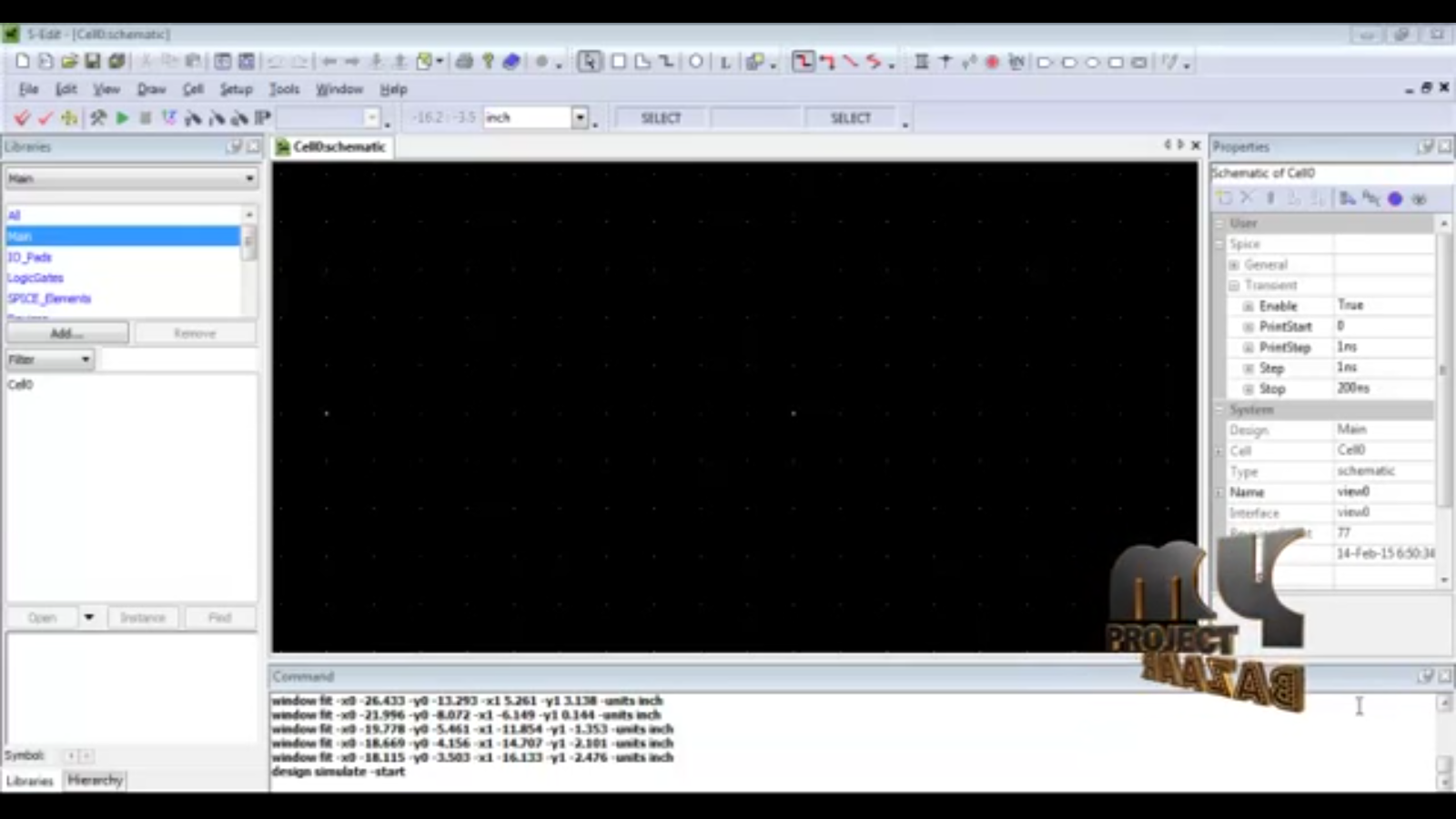

Abstract—Leakage power is a major issue for short channel devices. As the technology is shrinking (i.e., 180nm, 90nm, 45nm. etc.) the leakage current is increasing very fast. < Final Year Projects > So, several methods and techniques have been proposed for leakage reduction in CMOS digital integrated circuits. Leakage power dissipation has become a sizable proportion of the total power dissipation in integrated circuit. This paper demonstrates the ideas of 6T, 8T and 10T models with sleep transistors. This proposed SRAM cells give the advantages over basic 6T, 8T and 10T transistor models. The SRAM cell with sleep transistor shows better leakage reduction approach than stack approaches. Here in this paper Analog environment virtuoso (cadence) simulator is used for analysis of the power associated with CMOS SRAM cell for 180nm technology.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+