An Efficient VLSI Architecture for Data Encryption Standard and its FPGA Implementation

Product Description

An Efficient VLSI Architecture for Data Encryption Standard and its FPGA Implementation

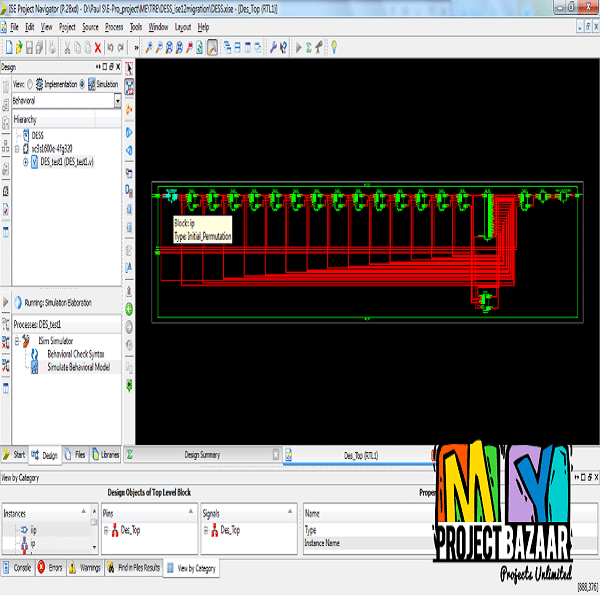

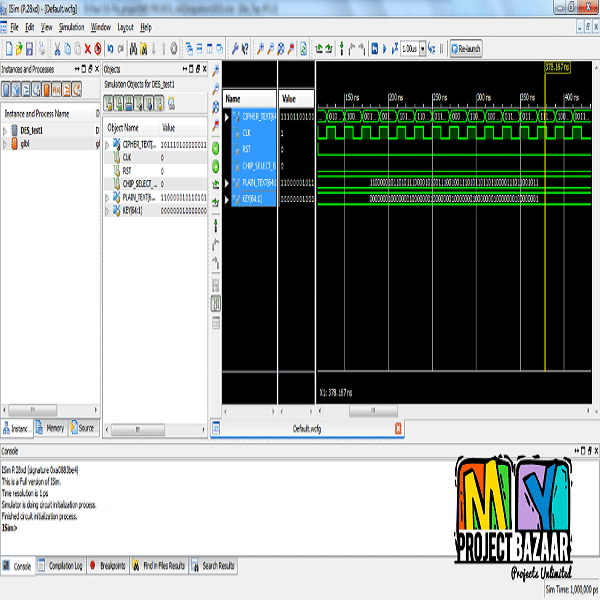

Abstract-To achieve the goal of secure communication,cryptography is an essential operation. Many applications, including health-monitoring and biometric data based recognition system, need short-term data security. To design short-term security based applications, there is an essential need of high-performance, low cost and area-efficient VLSI implementation of lightweight ciphers. Data encryption standard (DES) is well-suited for the implementation of low-cost lightweight cryptography applications. In this paper, we propose an efficient VLSI architecture for DES algorithm based encryption/decryption engine. Depending upon the encryption/decryption needs, the same set of architecture performs both encryption and decryption operations. In the implementation of DES algorithm, a chain of multiplexer-based architecture is used to implement the substitution operations (SBoxes).The proposed architecture is modeled in the VHDL design language and synthesized in the Xilinx Virtex-5 xc5vfx70t field-programmable gate array (FPGA) device. Hardware synthesis result shows that the proposed design utilizes only 1.07% slice LUTs, 0.31% slice registers and 29.22% of bonded IOBs of the FPGA device fabric.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+