Algorithm and Architecture for a Low-Power Content-Addressable Memory Based on Sparse Clustered Networks

Product Description

Algorithm and Architecture for a Low-Power Content-Addressable Memory Based on Sparse Clustered Networks

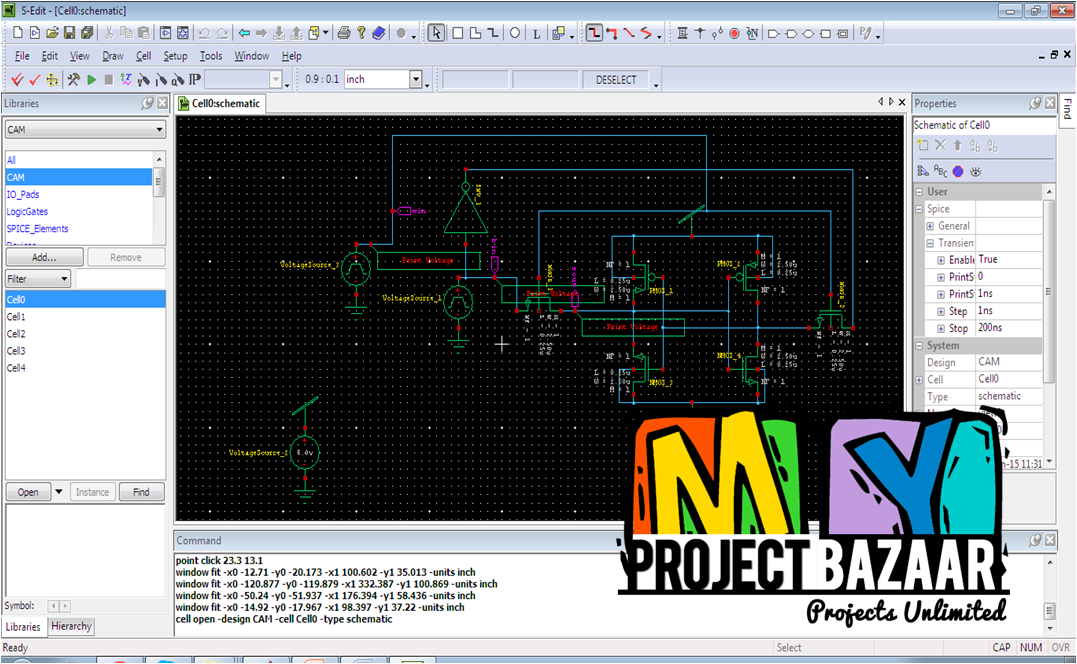

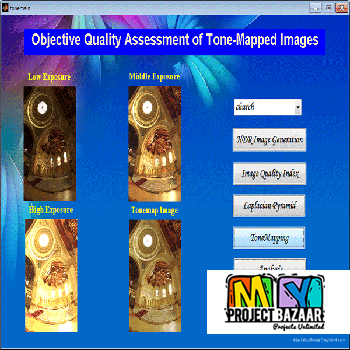

Abstract— Algorithm and Architecture for a Low-Power Content-Addressable Memory Based on Sparse Clustered Networks. A low-power content-addressable memory < Final Year Project 2016 > CAM employing a new algorithm for associativity between the input tag and the corresponding address of the output data. The proposed architecture is based on a recently developed sparse clustered network using binary connections that On -average eliminates most of the parallel comparisons performed during a search. Therefore, the dynamic energy consumption of the proposed design is significantly lower compared with that of a conventional low-power CAM design. Given an input tag, the proposed architecture computes a few possibilities for the location of the matched tag and performs the comparisons on them to locate a single valid match. TSMC 65-nm CMOS technology was used for simulation purposes.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|