Achieving Memory Access Equalization via Round-trip Routing Latency Prediction in 3D Many-core NoCs

Product Description

Achieving Memory Access Equalization via Round-trip Routing Latency Prediction in 3D Many-core NoCs

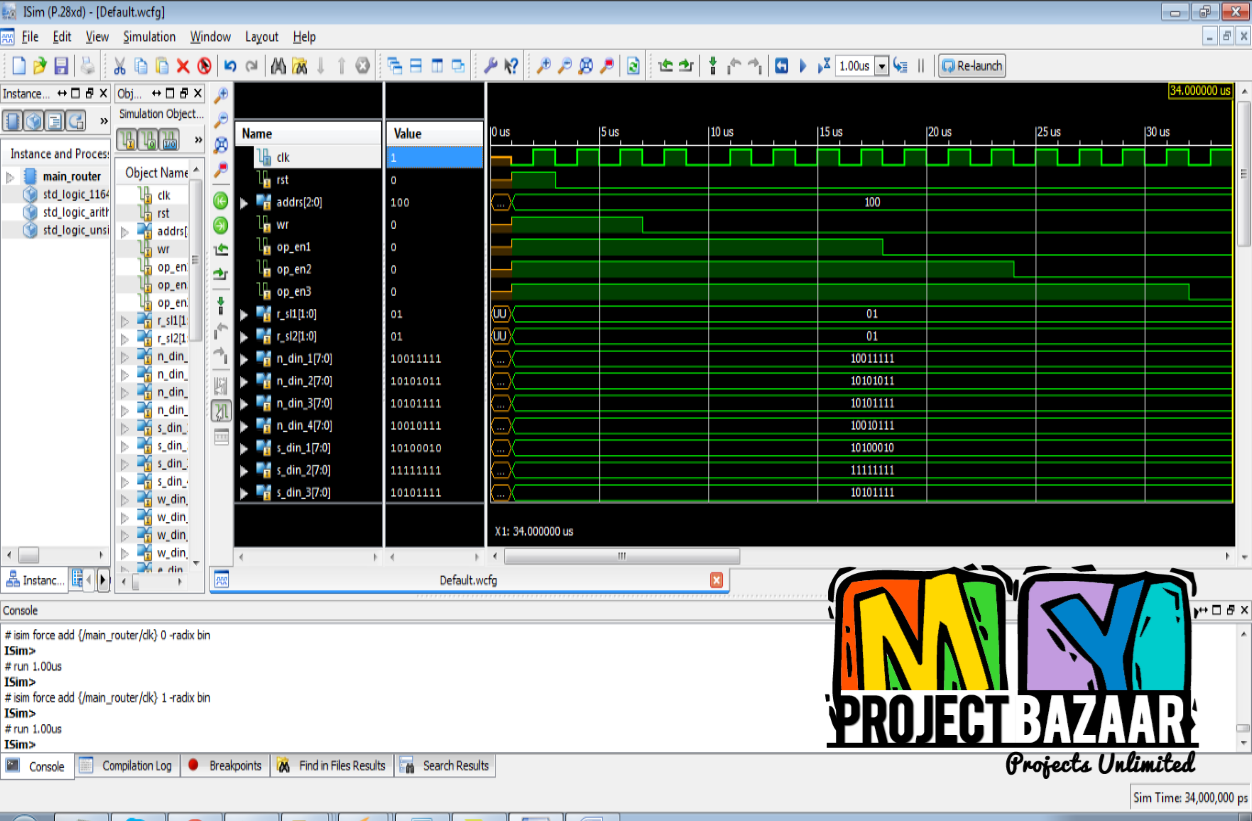

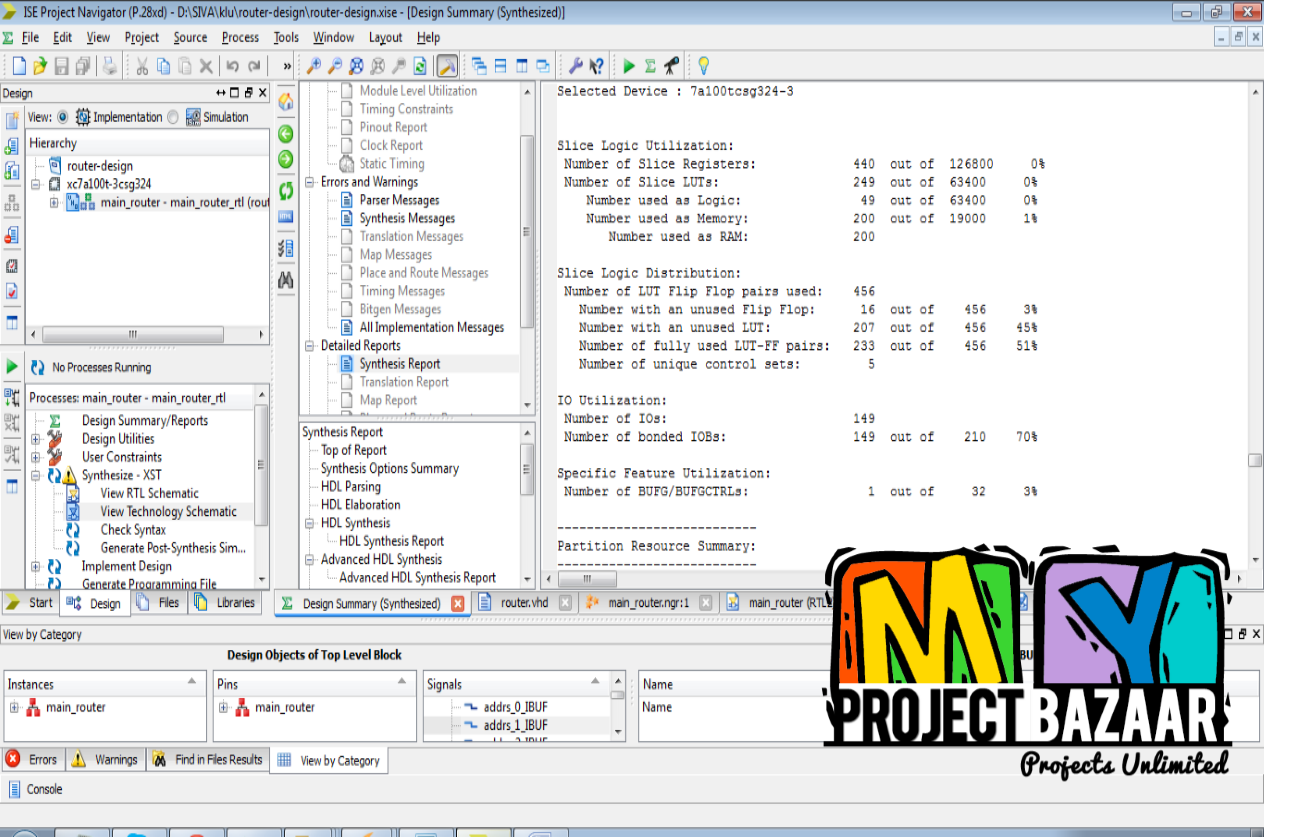

Abstract— 3D many-core NoCs are emerging architectures for future high-performance single chips due to its integration of many processor cores and memories by stacking multiple layers. In such architecture, because processor cores and memories reside in different locations (center, corner, edge, etc.), memory accesses behave differently due to their different communication distances, and the performance < Final Year Projects 2016 > gap of different memory accesses becomes larger as the network size is scaled up. This phenomenon may lead to very high latencies suffered from by some memory accesses, thus degrading the system performance. To achieve high performance, it is crucial to reduce the number of memory accesses with very high latencies. However, this should be done with care since shortening the latency of one memory access can worsen the latency of another as a result of shared network resources. Therefore, the goal should focus on narrowing the latency difference of memory accesses. We address the goal by proposing to prioritize the memory access packets based on predicting the round-trip routing latencies of memory accesses.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|