An 8-bit 100-GS/s Distributed DAC in 28-nm CMOS for Optical Communications

Product Description

An 8-bit 100-GS/s Distributed DAC in 28-nm CMOS for Optical Communications

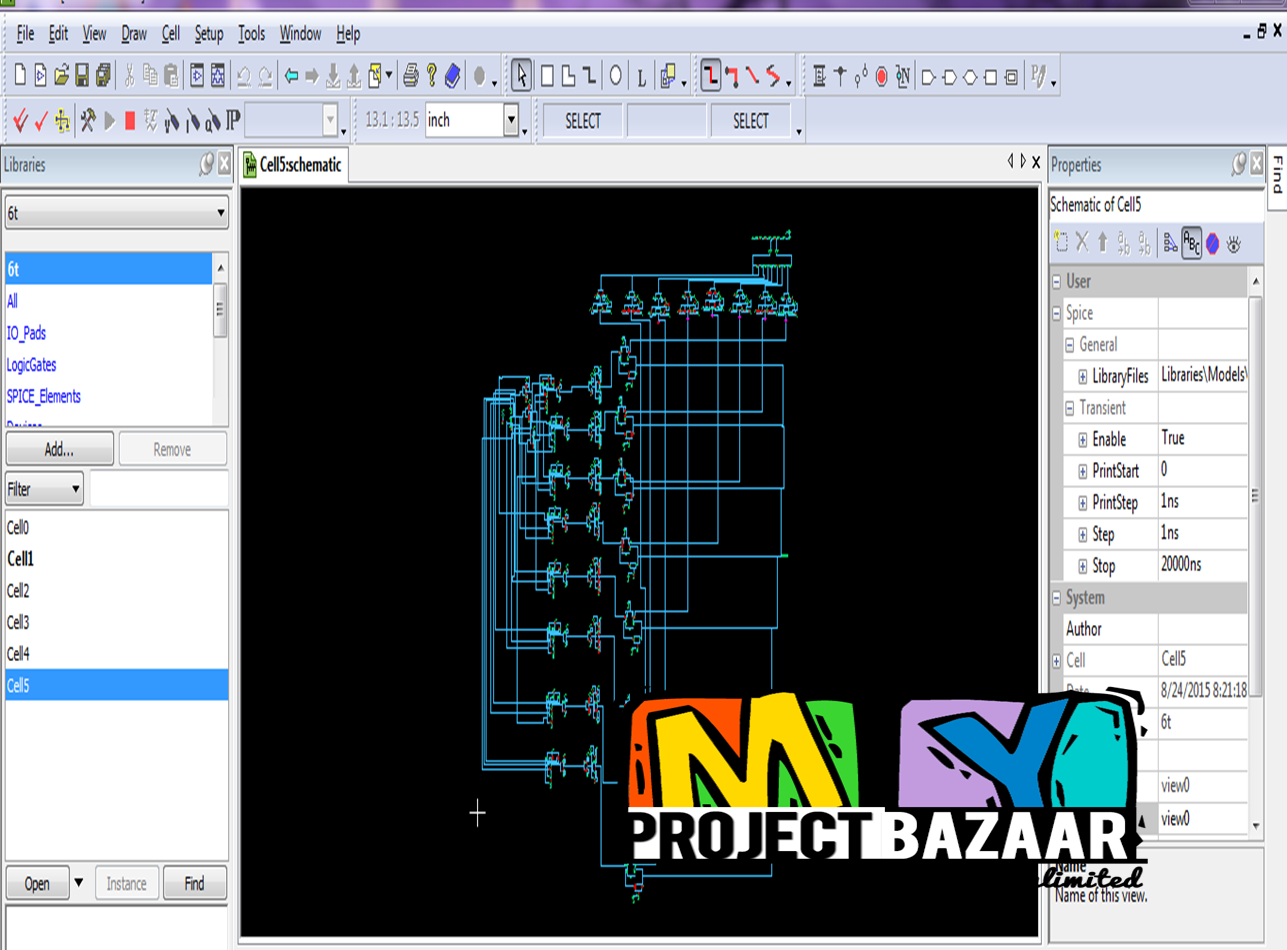

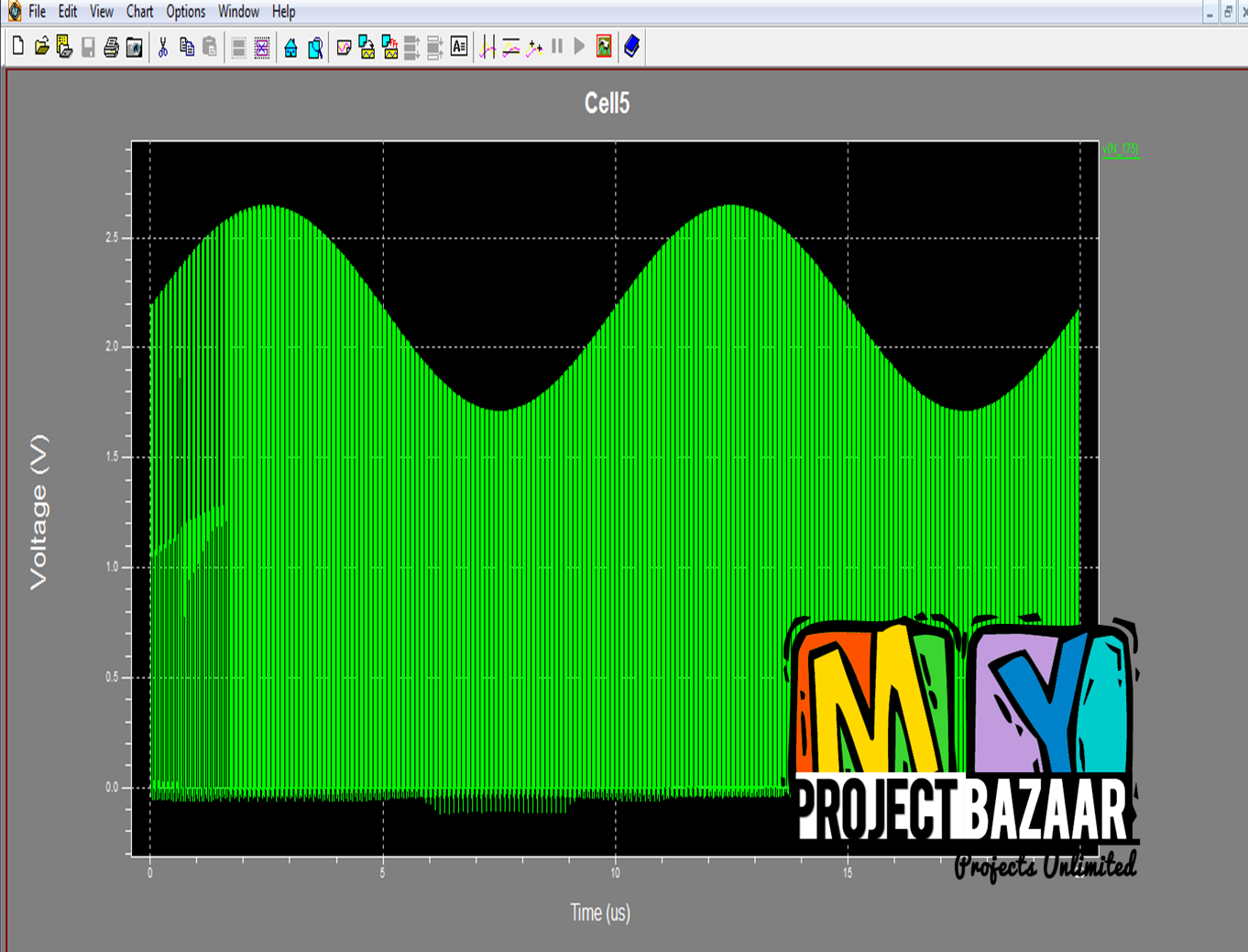

Abstract—An 8-bit 100-GS/s digital-to-analog converter < Final Year Projects 2016 > DAC using a distributed output topology in 28-nm low-power CMOS for optical communications is presented. The DAC can convert 1-k symbols stored in the 1-kbyte design-for-test on-chip memory cyclically. By interleaving four 25-GS/s return-to-zero DACs, the highest signal frequency of the 100-GS/s DAC is about 25 GHz and the output image is located beyond 75 GHz. The 3-dB bandwidth exceeds 13 GHz at 100 GS/s. The effective number of bits and spurious-free dynamic range ranges from 5.3 bit and 41 dB to 3.2 bit and 27 dB from dc up to 24.9 GHz at 100 GS/s, respectively. Transmission rates of 120 and 45 Gb/s are obtained in an electrical and an optical back-to-back experiment, respectively. The DAC test chip consumes 2.5 W from a power supply with multiple outputs of 1.1, 1.5, and 2 V

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|