A 65 nm Cryptographic Processor for High Speed Pairing Computation

Product Description

A 65 nm Cryptographic Processor for High Speed Pairing Computation

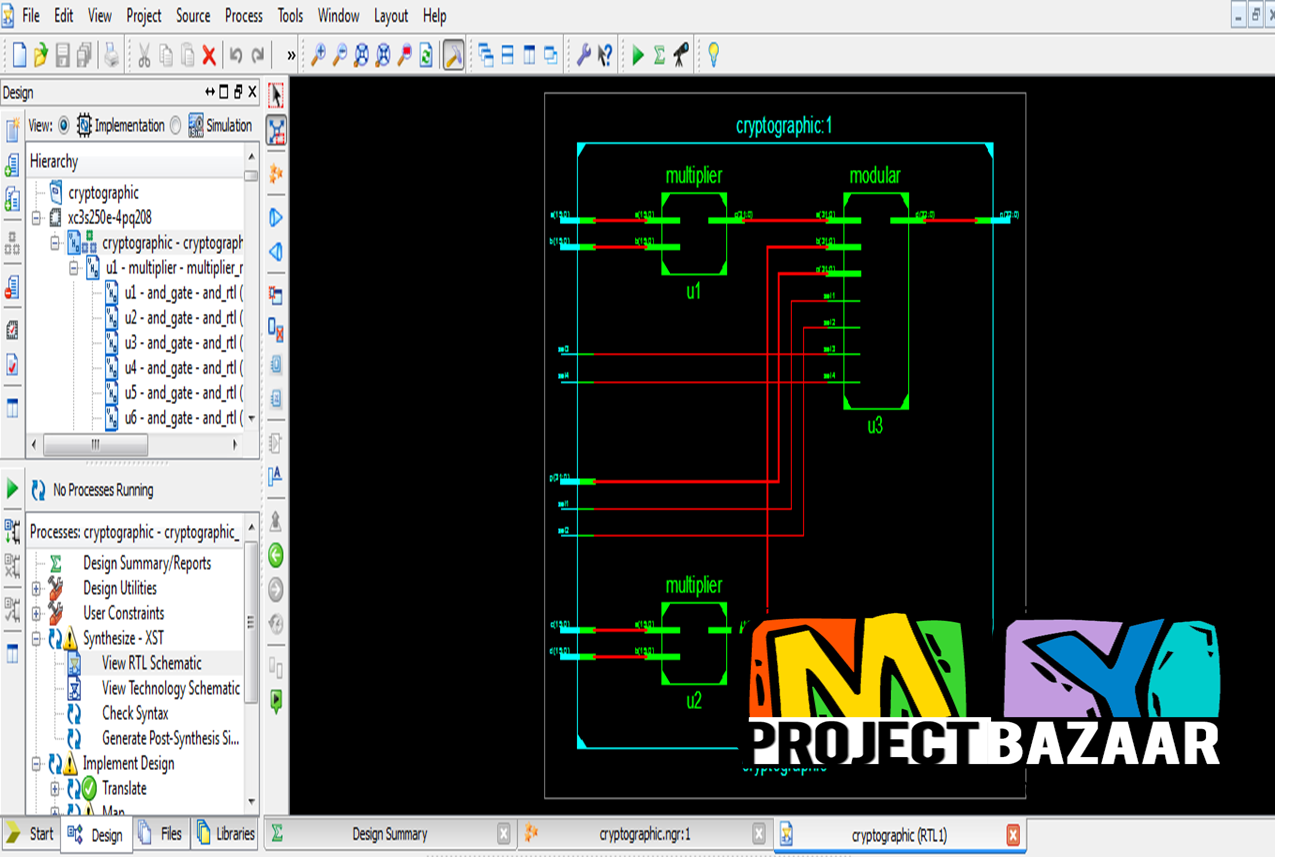

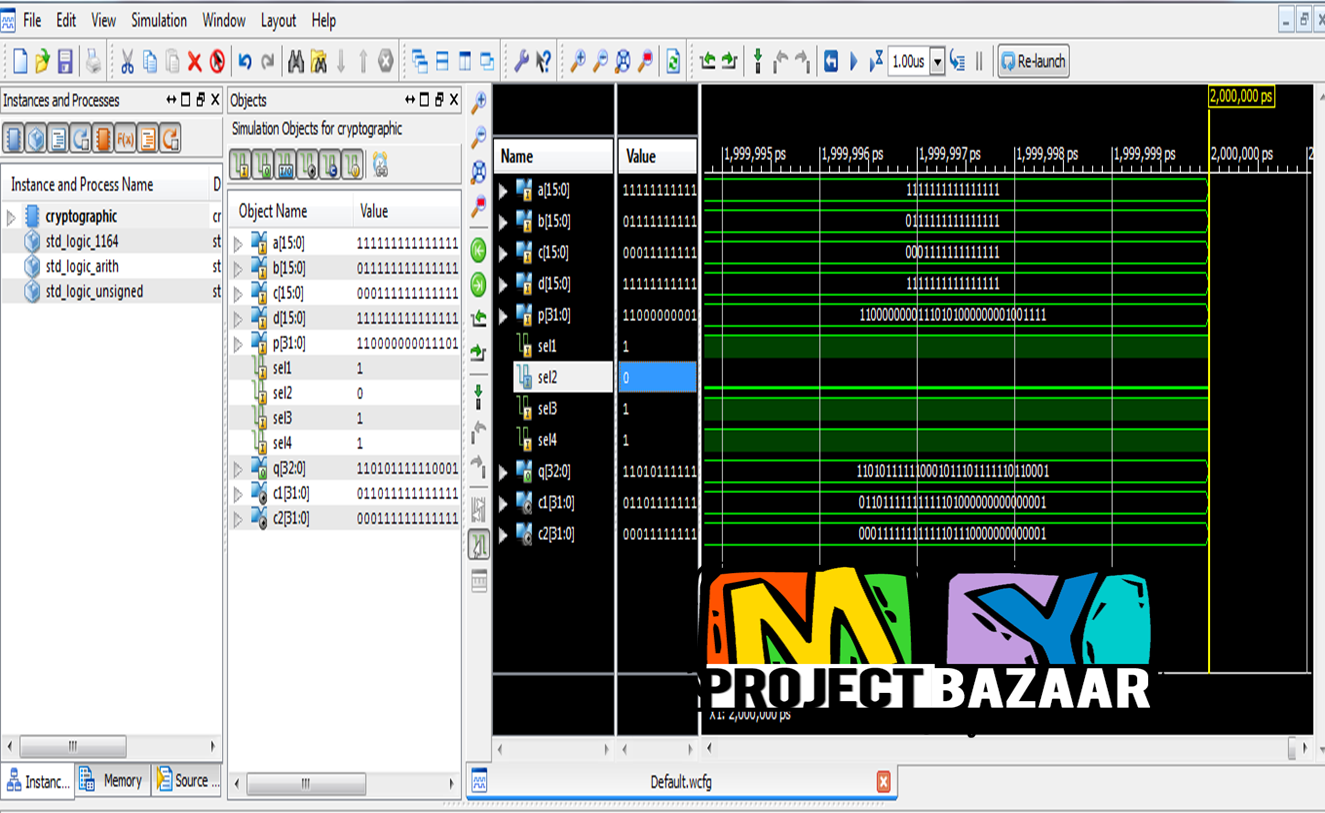

Abstract— A 65 nm Cryptographic Processor for High Speed Pairing Computation. Pairings are attractive and competitive cryptographic primitives for establishing various novel and powerful information security schemes. This paper presents a flexible and high-performance processor for cryptographic pairings over pairing-friendly curves at high security levels. In this design, hardware for F arithmetic is optimized to accelerate the pairing computation, and especially a combined modular multiplier, p2 which implements ( AB + CD) mod P based on Montgomery method, is proposed. < Final Year Project 2016 >This combined multiplier has the data path delay close to that of a single multiplier implementing AB mod P but saves 20% area cost compared with two single multipliers.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|