A 16 Kb Spin-Transfer Torque Random Access Memory With Self-Enable Switching and Precharge Sensing Schemes

Product Description

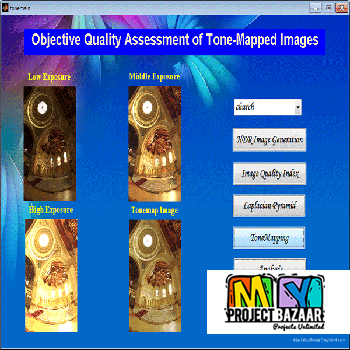

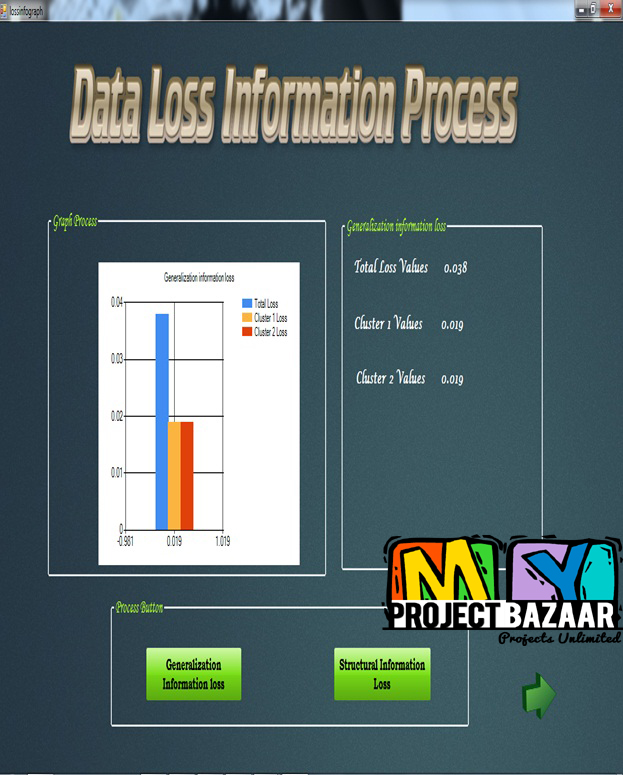

Abstract—Spin-transfer torque magnetic random access memory (STT-MRAM) is considered one of the most promising non-volatile memory candidates thanks to its excellent performance in terms of access speed, endurance, and compatibility to CMOS. However, high power supply voltage is required in the conventional STT-MRAM writing circuit, which results in high power consumption (e.g., ~10 pJ/bit). In addition, it suffers from stochastic switching behavior and process voltage temperature variations. < Final Year Projects > These make power-efficient and reliable write/read circuits become critical challenges. In this paper, we present novel circuits and architectures to build a 16 kb STT-MRAM design with low power and high reliability. For example, the self-enable switching scheme reduces the power consumption effectively and the fore-placed sense amplifier improves the robustness to process variation. Using an accurate compact model of 65 nm STT-MRAM and a commercial CMOS design kit, mixed transient and statistical simulations have been performed to validate this design.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet