A 6 b 5 GS/s 4 Interleave d 3 b/Cycle SAR ADC

Product Description

A 6 b 5 GS/s 4 Interleave d 3 b/Cycle SAR ADC

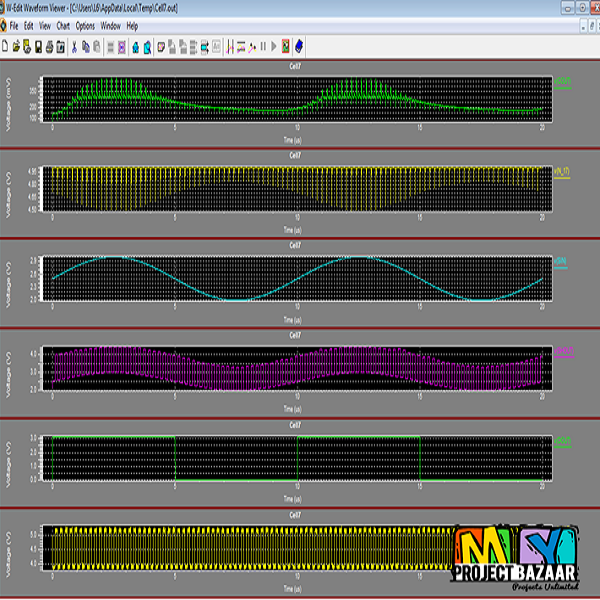

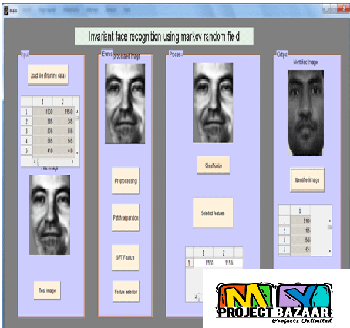

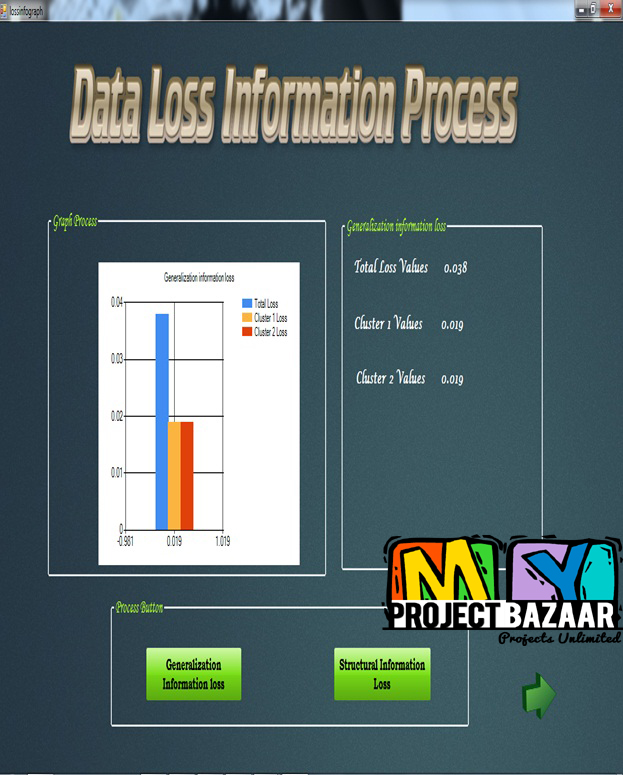

Abstract—This paper presents a 4× time-interleaved 6-bit 5 GS/s 3 b/cycle SAR analog-to-digital converter (ADC). Hardware overhead induced by a 3 b /cycle architecture is eased by an interpolation technique where around 1/3 of the hardware is saved. In addition, complicated switching controls are simplified with a proposed fractional DAC array s witching scheme, thus reducing t he design complexity and the hardware burden. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|