A 40–170 MHz PLL-Based PWM Driver Using 2-/3-/5-Level Class-D PA in 130 nm CMOS

Product Description

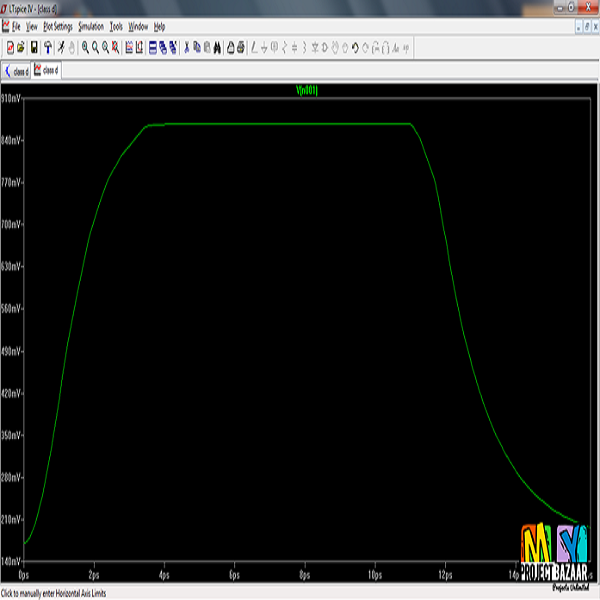

A 40–170 MHz PLL-Based PWM Driver Using 2-/3-/5-Level Class-D PA in 130 nm CMOS

Abstract— A high-speed driver that provides a pulsewidth modulated output while using a class-D Power Amplifier (PA) is described. A PLL-based architecture is employed, which eliminates the requirement for a precise ramp or triangular signal generator, and a high-speed comparator, which are typically used in pulsewidth modulation (PWM) generation. < final year projects >

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|