Scan Test Bandwidth Management for Ultralarge-Scale System-on-Chip Architectures

Product Description

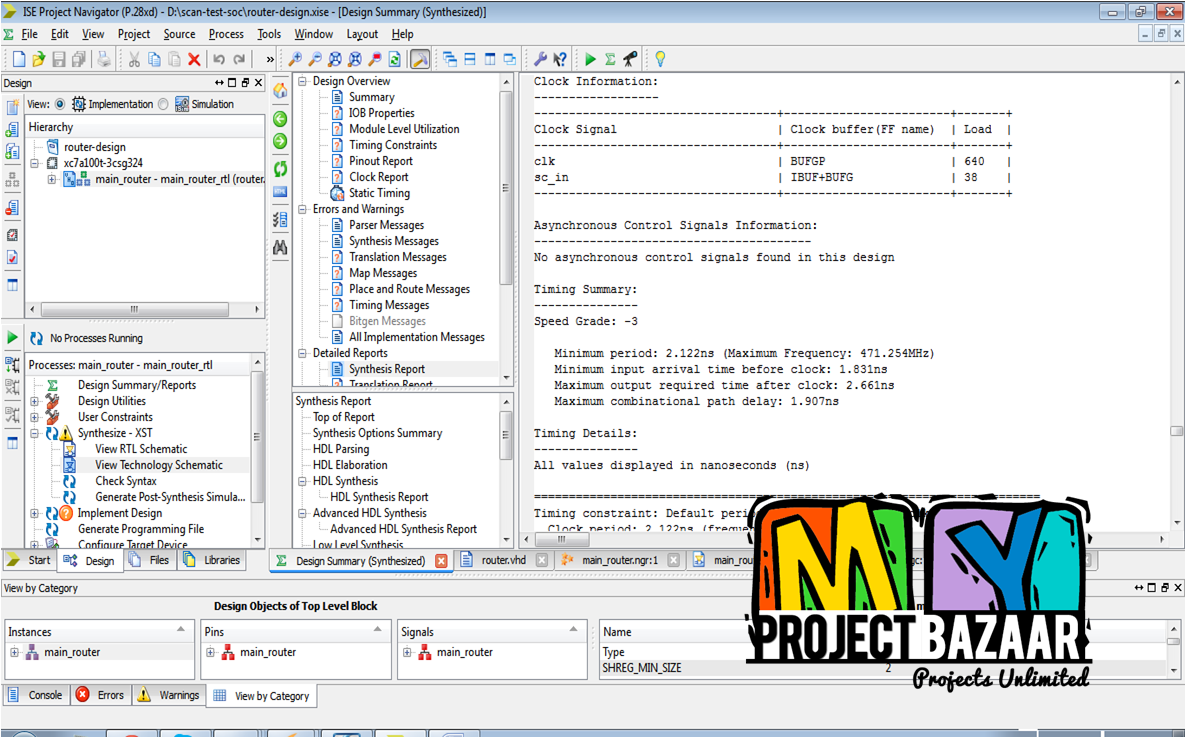

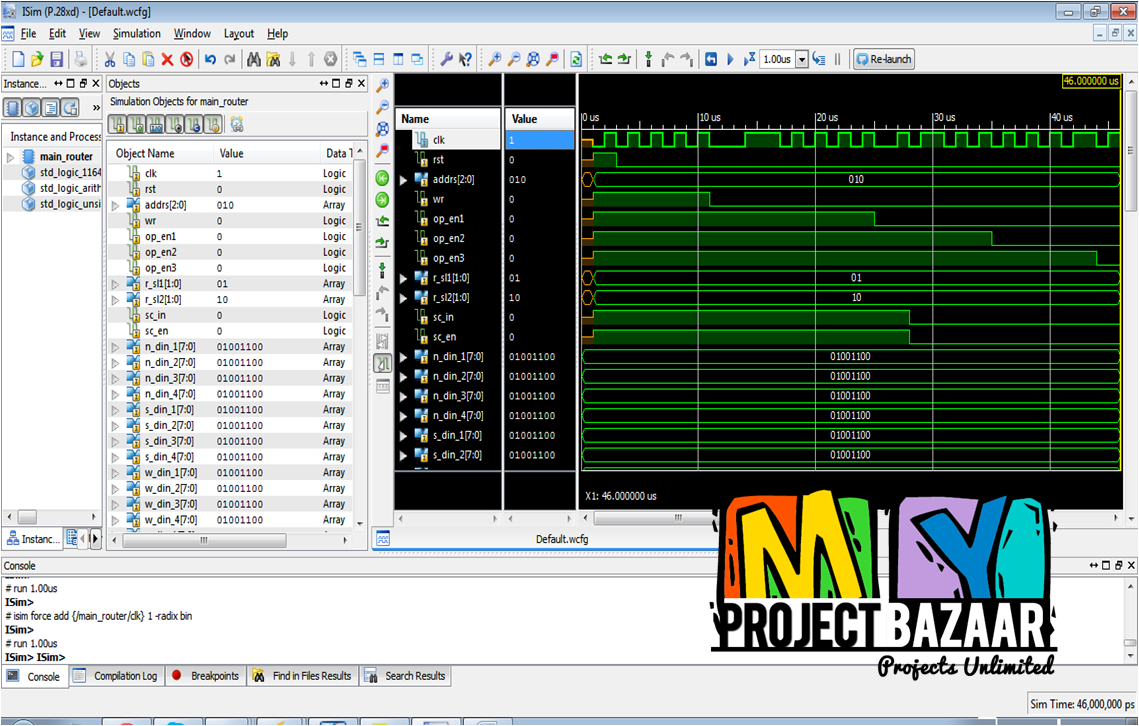

Scan Test Bandwidth Management for Ultralarge-Scale System-on-Chip Architectures

Abstract— Scan Test Bandwidth Management for Ultralarge-Scale System-on-Chip Architectures. Presents several techniques employed to resolve problems surfacing when applying scan bandwidth management to large industrial multicore system-on-chip < Final Year Projects 2016 > SoC designs with embedded test data compression. These designs pose significant challenges to the channel management scheme, flow, and tools. This paper introduces several test logic architectures that facilitate preemptive test scheduling for SoC circuits with embedded deterministic test-based test data compression. The same solutions allow efficient handling of physical constraints in realistic applications. Finally, state-of-the-art SoC test scheduling algorithms are rearchitected accordingly by making provisions for: 1) setting up time-effective test configurations; 2) optimization of SoC pin partitions; 3) allocation of core-level channels based on scan data volume; and 4) more flexible core-wise usage of automatic test equipment channel resources. A detailed case study is illustrated herein with a variety of experiments allowing one to learn how to tradeoff different architectures and test-related factors.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Additional Information

| Domains |

|---|

Would you like to submit yours?

There are no reviews yet