Scalable Application-Dependent Diagnosis of Interconnects of SRAM-Based FPGAs

Product Description

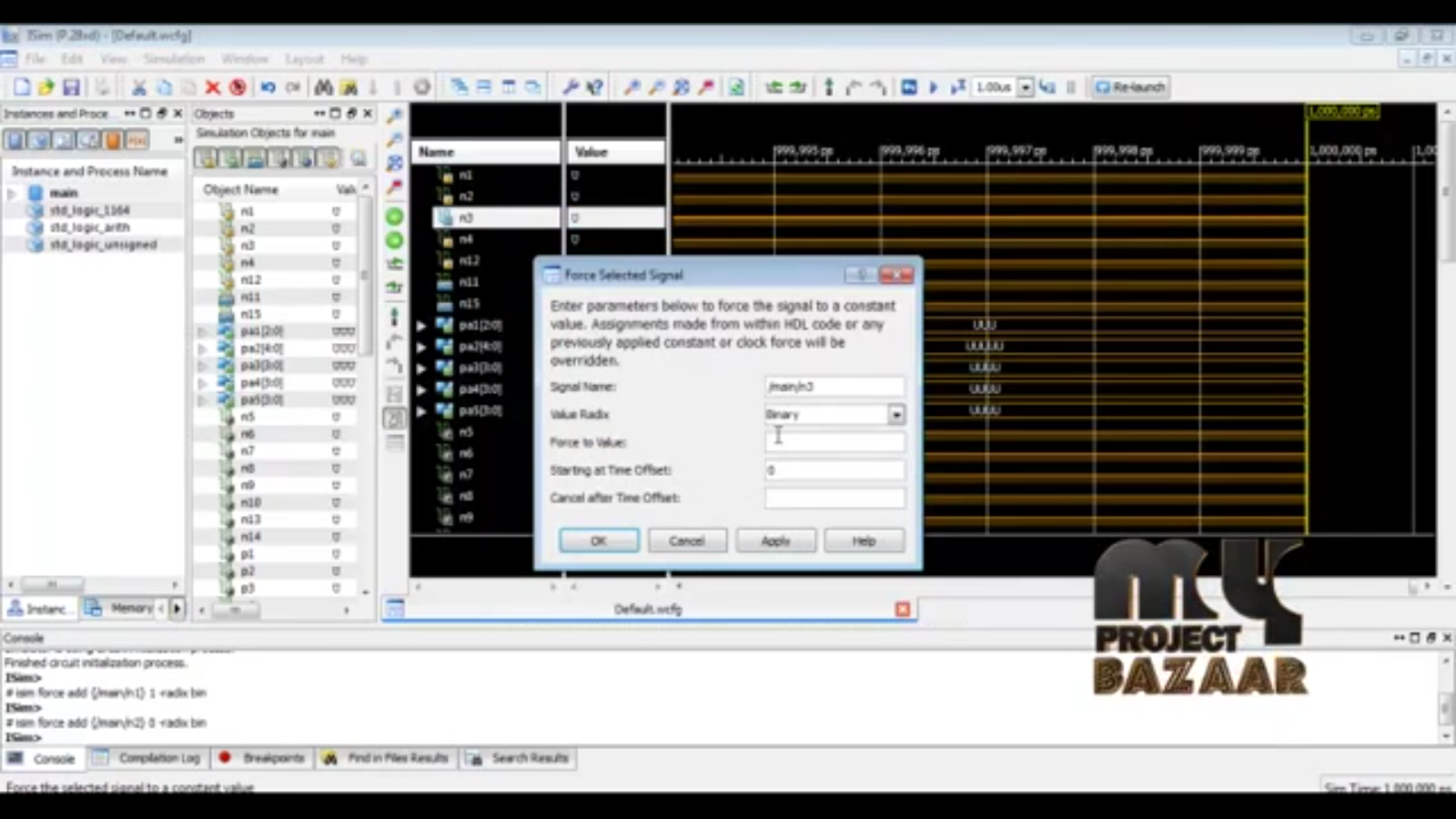

Abstract—This paper presents a new method for diagnosing (detection and location) multiple faults in an application-dependent interconnect of a SRAM-based FPGA. For fault detection, the proposed technique retains the original interconnect configuration and modifies the function of the LUTs using the new LUT programming function 1-Bit Sum Function (1-BSF); in addition, it utilizes features such as branches in the nets as well as the primary (unused) IOs of the FPGAs. < Final Year Projects > The proposed method detects all possible stuck-at and bridging faults of all cardinalities in a single configuration; fault detection requires 1 + log2k test configurations for multiple stuck-at location and 2 + 2log2k additional test configurations to locate more than one pair-wise bridging faults (where k denotes the maximum combinational depth of the FPGA circuit). Following detection, the locations of multiple faults are hierarchically identified using the walking-1 test set and an adaptive approach for the interconnect structure. Net ordering independence is accomplished by utilizing features such as the presence of paths of nets that are either disjoint or joint between the primary input and at least one primary output. As validated by simulation on benchmark circuits, the proposed method scales extremely well for different Virtex FPGA families; this results in a significant reduction in the number of configurations for diagnosing multiple faults.

Including Packages

Our Specialization

Support Service

Statistical Report

satisfied customers

3,589

Freelance projects

983

sales on Site

11,021

developers

175+Would you like to submit yours?

There are no reviews yet